IP Core per dispositivi USB3 Vision

IP Core per dispositivi USB3 Vision per FPGA

- Compatibile con AMD Serie 7 (e successive)

- Compatibile con dispositivi Altera Cyclone V (e successivi)

- Compatto

- Personalizzabile

- Fornito come progetto di riferimento funzionante

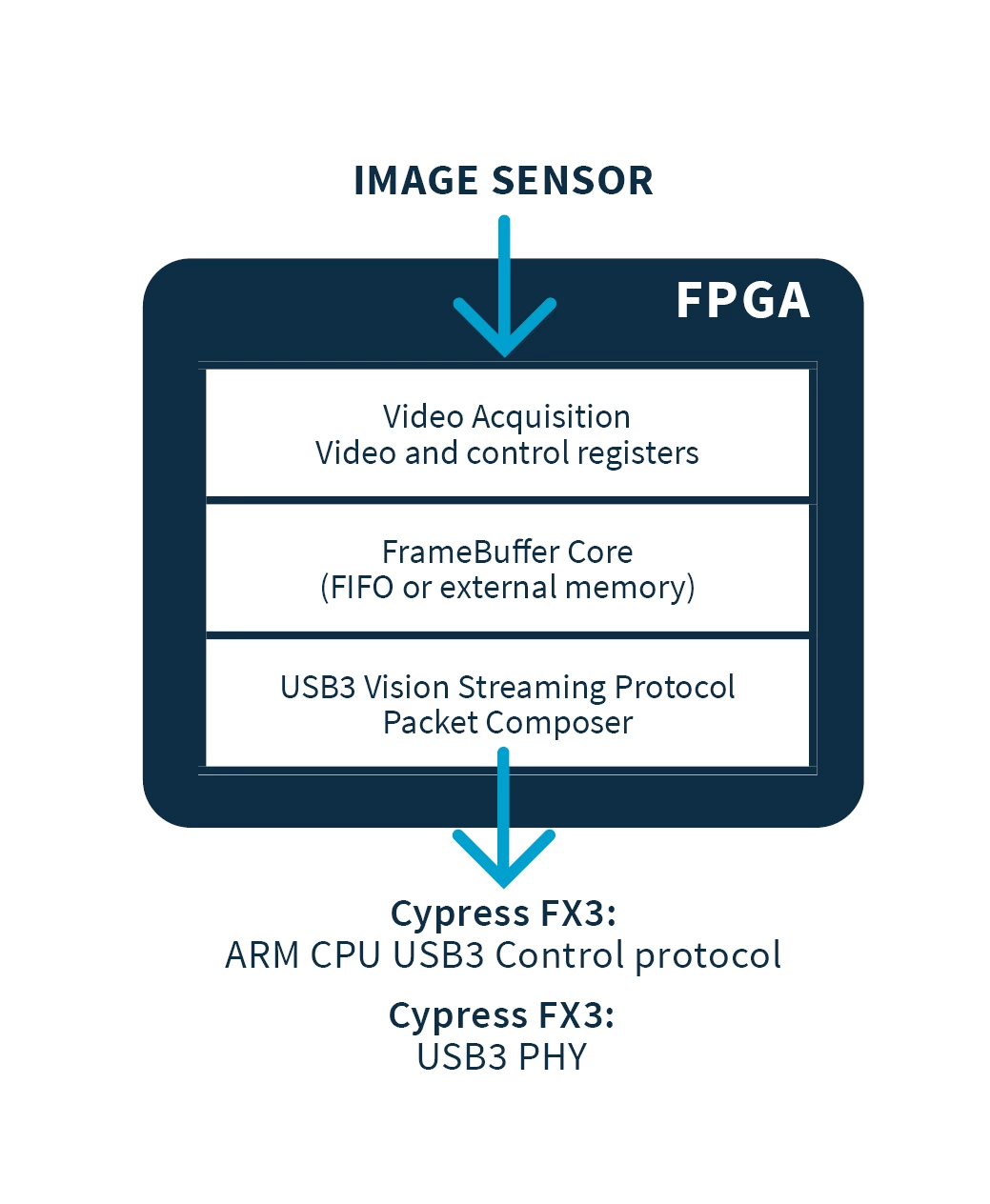

Architettura

USB3 Vision è un protocollo di comunicazione standard per applicazioni di visione basato sull'interfaccia USB 3.0 ampiamente utilizzata. Essendo un protocollo standard e supportando GenICam, consente un facile collegamento tra telecamere e PC. Sensor to Image offre una serie di IP Cores e un framework di sviluppo per realizzare prodotti basati su FPGA utilizzando l'interfaccia USB3 Vision. Data la velocità di USB3 Vision, i dispositivi di trasmissione e ricezione richiedono un'implementazione veloce basata su FPGA del core USB integrato. Gli IP Core USB3 Vision sono compatibili con i dispositivi AMD Serie 7 (e successivi) e Altera Cyclone V (e successivi).

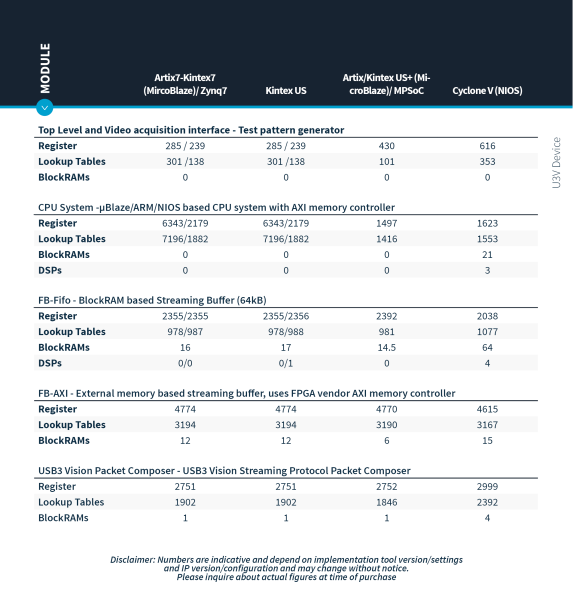

Utilizzo delle risorse

Scarica l'utilizzo delle risorseVantaggi

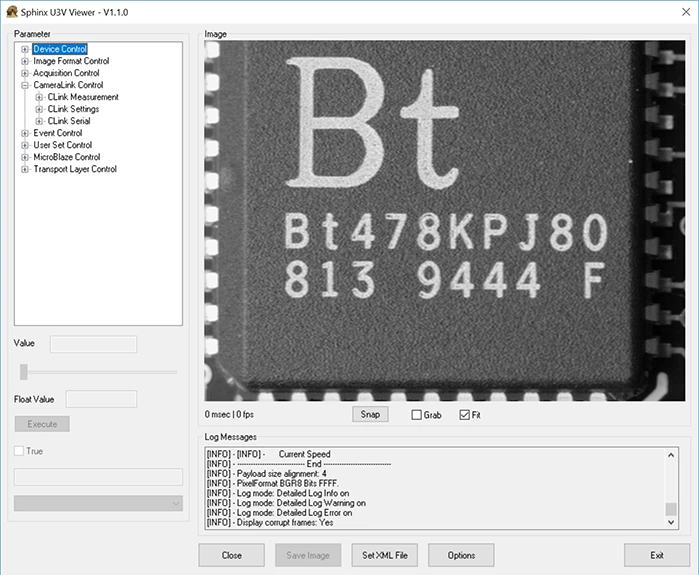

SDK Sphinx incluso

Sphinx è un toolkit software ricco di funzionalità che fornisce gli elementi fondamentali per progettare in modo semplice e veloce applicazioni video ad alte prestazioni che utilizzano risorse CPU minime. Il toolkit include anche un Driver software per dispositivi USB3 Vision e una libreria di acquisizione per Windows o Linux, oltre ad applicazioni di esempio, tra cui un visualizzatore conforme a USB3 Vision/Genicam.

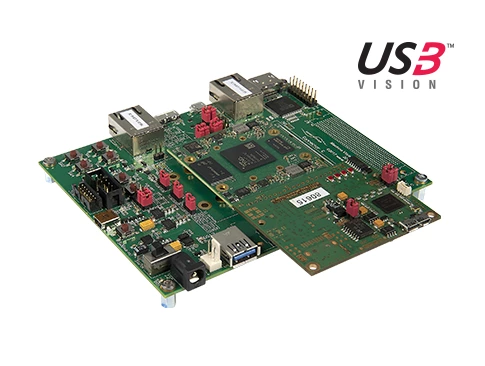

Kit di sviluppo per visione artificiale MVDK per USB3 Vision

Il kit di sviluppo MVDK di Sensor to Image è una piattaforma di valutazione flessibile per applicazioni di visione artificiale. Supporta i progetti di dispositivi USB3 Vision per vari moduli FPGA Enclustra con FPGA Altera e AMD.

Codice sorgente C per libreria software

L'IP Core USB3 Vision offre la possibilità di utilizzare il codice sorgente della libreria USB3 Vision integrata in esecuzione sul controller USB Cypress FX3. Ciò è utile per estendere le funzionalità delle caratteristiche USB3 Vision opzionali utilizzate raramente o per adattare meglio i requisiti hardware.

Progetto di riferimento fornito

La soluzione USB3 Vision FPGA di S2I viene fornita come progetto di riferimento completamente funzionante insieme agli IP Cores FPGA. Ciò riduce al minimo i tempi di sviluppo e garantisce prestazioni eccellenti con un ingombro ridotto, lasciando al contempo sufficiente flessibilità per personalizzare il progetto. I core Sensor to Image sono compatti e lasciano spazio sufficiente nell'FPGA per la vostra applicazione.

Progettazione di alto livello

Il primo componente dell'IP Core è il Top Level Design. Si tratta di un'interfaccia tra l'hardware esterno (imager, sensori, USB3 PHY) e l'elaborazione dei dati interna dell'FPGA. Forniamo questo modulo come codice sorgente VHDL e può essere adattato all'hardware personalizzato.

Framebuffer Core

Un frame buffer si interfaccia con il controller di memoria specifico del fornitore FPGA. Il frame buffer consente il buffering dei dati e la partizionatura delle immagini. Questo modulo utilizza tipicamente la memoria interna dell'FPGA, ma in alternativa è possibile utilizzare una memoria esterna per livellare i ritardi di comunicazione più lunghi tra la telecamera e il PC.

Modulo di acquisizione video

Il modulo di acquisizione video del progetto di riferimento simula una telecamera con un generatore di pattern di prova. Questo modulo viene fornito come codice sorgente VHDL, che deve essere sostituito da un'interfaccia sensore e da una logica di elaborazione dei pixel nel progetto finale della telecamera.

Compositore di pacchetti del protocollo di streaming USB3 Vision

Il compositore di pacchetti del protocollo USB3 Vision Streaming prende tutti i dati dalla sorgente video e crea i pacchetti USB3 Vision streaming. Gestisce anche tutte le comunicazioni di basso livello con USB3 PHY (Cypress FX3).

Cypress FX3

Un chip Cypress FX3 (con CPU ARM integrata e interfaccia fisica) viene utilizzato per gestire tutte le routine di inizializzazione USB3 e la comunicazione del canale di controllo USB3 Vision.