IP Core del dispositivo GigE Vision

IP Core GigE Vision Device per FPGA

- Compatto

- Personalizzabile

- Compatibile con AMD Serie 7 (e successive)

- Compatibile con dispositivi Altera Cyclone V (e successivi)

- Compatibilità preliminare con Microchip PolarFire

- Supporto di velocità da 1 Gbps a oltre 10 Gbps

- Fornito come progetto di riferimento autonomo e completamente funzionante

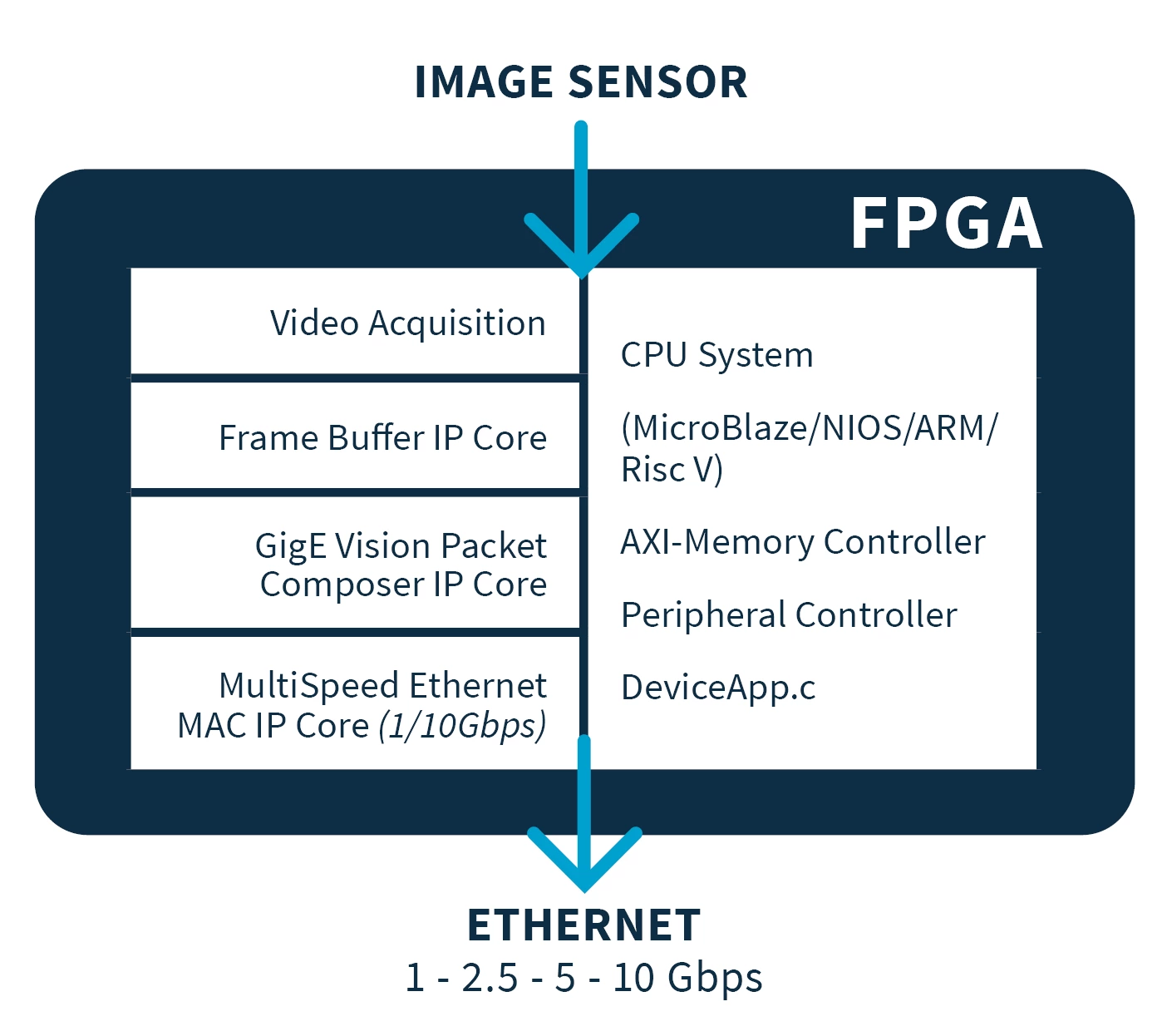

Architettura

GigE Vision è un protocollo di comunicazione standard per applicazioni di visione basato sulla nota tecnologia Ethernet. Consente un facile interfacciamento tra dispositivi GigE Vision e PC che eseguono la famiglia di protocolli TCP/IP. Sensor to Image offre una serie di IP Cores e un framework di sviluppo per realizzare prodotti trasmettitori basati su FPGA utilizzando l'interfaccia GigE Vision. A causa della velocità di GigE Vision, specialmente a velocità superiori a 1 Gbps, i mittenti richiedono un'implementazione veloce basata su FPGA del core GigE incorporato. Il set di core GigE Vision è compatibile con i dispositivi AMD Serie 7 (e successivi), i dispositivi Altera Cyclone V (e successivi) e Microchip PolarFire.

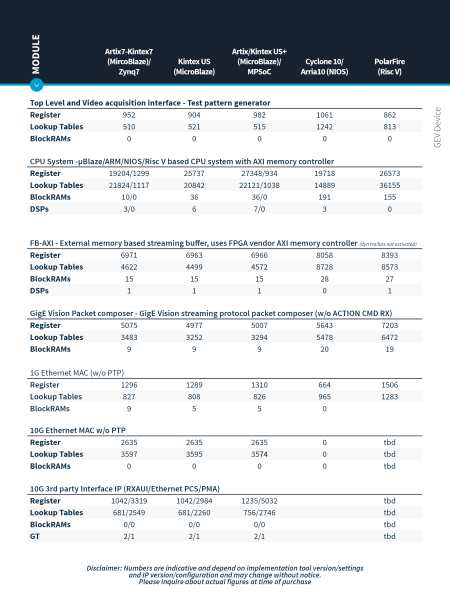

Utilizzo delle risorse

Scarica l'utilizzo delle risorseVantaggi

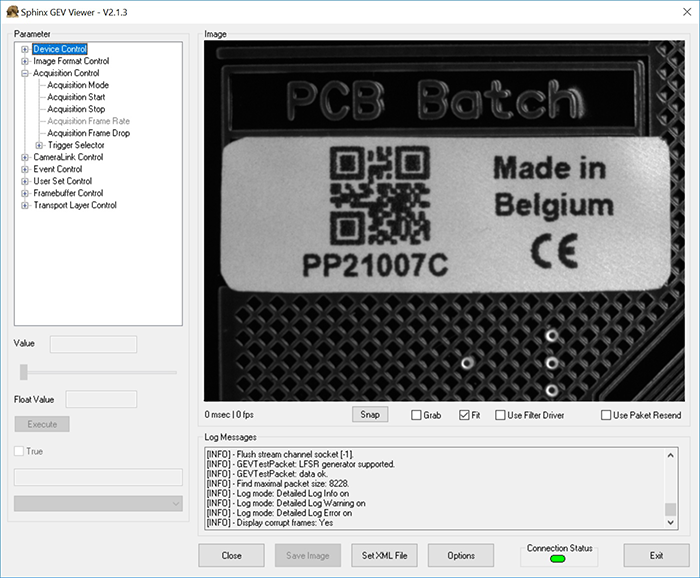

SDK Sphinx incluso

Un toolkit software ricco di funzionalità che fornisce gli elementi fondamentali per progettare in modo semplice e veloce applicazioni video ad alte prestazioni che utilizzano risorse CPU minime. Include anche un Driver software filtro e una libreria di acquisizione per Windows o Linux, oltre ad applicazioni di esempio, tra cui un visualizzatore conforme a GigE Vision/GenICam.

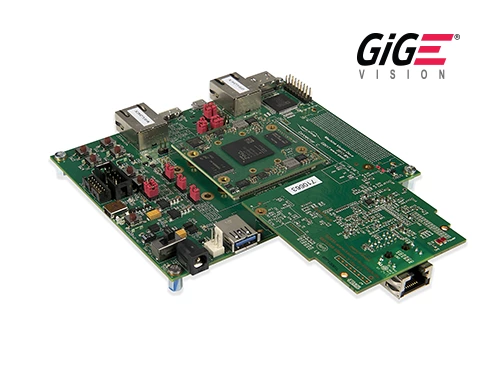

Ampio supporto dei kit di sviluppo FPGA

IP Cores di Sensor to Image vengono forniti come progetti di riferimento completamente funzionanti su un kit di sviluppo FPGA. Supportiamo un'ampia gamma di kit standard di AMD, Altera e Microchip.

Assistenza GenDC

Il GigE Vision IP Core offre la possibilità di supportare il tipo di payload GenDC, potente e molto flessibile. Ciò è utile per trasferire strutture di dati complesse spesso utilizzate nelle applicazioni 3D.

Progetto di riferimento fornito

Progetto di riferimento completamente funzionante: le soluzioni FPGA di S2I vengono fornite come progetto di riferimento autonomo e completamente funzionante, che gira su una piattaforma comune concordata insieme agli IP Cores FPGA. Questo riduce al minimo i tempi di sviluppo e garantisce prestazioni eccellenti con un ingombro ridotto, lasciando al contempo sufficiente flessibilità per personalizzare il progetto. I core Sensor to Image sono compatti e lasciano spazio sufficiente nell'FPGA per la vostra applicazione.

Decodificatore di comandi ACTION a bassa latenza

Il GigE Vision IP Core offre l'opzione di un decodificatore implementato hardware per il comando GigE Vision ACTION. Ciò consente trigger ad hoc a bassa latenza e basso jitter.

Progettazione di alto livello

Il primo componente dell'IP Core è il Top Level Design. Si tratta di un'interfaccia tra l'hardware esterno (imager, sensori, GigE PHY) e l'elaborazione dati interna dell'FPGA. Forniamo questo modulo come codice sorgente VHDL che può essere adattato all'hardware personalizzato.

CPU integrata FPGA

Per diverse attività di rete e configurazione non critiche in termini di tempo viene utilizzato un design CPU integrato FPGA (MicroBlaze, NIOS, ARM, Risc V). Implementa inoltre il GigE Vision Control Protocol (GVCP). Questo software è scritto in C e può essere esteso dal cliente.

Supporto multistream

Il GigE Vision IP Core offre la possibilità di trasferire più flussi di dati su un unico collegamento. Ciò è utile per trasferire dati non correlati provenienti da diverse fonti tramite un unico cavo.

Modulo di acquisizione video

Il modulo di acquisizione video del progetto di riferimento simula una telecamera con un generatore di pattern di prova. Questo modulo viene fornito come codice sorgente VHDL, che deve essere sostituito da un'interfaccia sensore e da una logica di elaborazione dei pixel nel progetto finale della telecamera.

Configurazione personalizzata

Alcune parti del progetto vengono fornite solo come file binari (ad esempio la libreria del protocollo di controllo GigE Vision), mentre altre parti vengono fornite come codice sorgente. Il framework di progettazione include tutti i file di progettazione e i core necessari, i file di progetto Vivado o Quartus. È configurato come un sistema di telecamere GigE Vision con un generatore di pattern di test configurabile. Questo sistema viene fornito come progetto di riferimento per una scheda di valutazione standard. Il progetto di riferimento utilizza gli strumenti di sviluppo AMD o Altera (non inclusi nella fornitura).

Framebuffer

Un framebuffer si interfaccia con il controller di memoria specifico del fornitore dell'FPGA. Il framebuffer consente il buffering dei frame e il packetizing delle immagini. Ciò è necessario per implementare la funzione di reinvio dei pacchetti. Questo modulo utilizza tipicamente memoria esterna, ma potrebbe anche essere realizzato con funzionalità limitate dalla memoria interna dell'FPGA.

Codice sorgente C per libreria software

La libreria GigE Vision integrata nell'IP Core GigE Vision può essere fornita opzionalmente come codice sorgente. Ciò è utile per estendere le funzionalità delle caratteristiche GigE Vision opzionali utilizzate raramente o per adattare meglio i requisiti hardware. Un Driver software aggiuntivo consente l'uso di Linux sul dispositivo.

Compositore di pacchetti GigE

Il GigE Packet Composer genera i pacchetti di flusso finali con tutte le intestazioni richieste dal livello di trasporto GigE Vision. Il GigE Packet Composer invia tutti i dati al MAC Ethernet e implementa il protocollo GigE Vision Streaming Protocol (GVSP) ad alta velocità.

Supporto IEEE1588

Il GigE Vision IP Core offre la possibilità di sincronizzare la propria base temporale con una sorgente temporale IEEE1588 esterna. Ciò è necessario per garantire un trigger temporale preciso senza cablaggi aggiuntivi. Quando non è disponibile alcuna sorgente temporale esterna, il sistema stesso può fungere da sorgente temporale.

MAC

Un componente MAC si interfaccia con la tecnologia del livello di trasporto di basso livello e con il livello fisico. È disponibile per diverse velocità da 1 Gbps fino a 10 Gbps e può supportare la marcatura dei pacchetti secondo il protocollo IEEE1588.

Estensioni dell'interfaccia FMC

Per ampliare le funzionalità delle varie schede di riferimento, forniamo schede FMC per Ethernet 1G e Ethernet 10G con supporto NBaseT.