CoaXPress Host IP Core

CoaXPress Host IP Core For FPGA

- Compatible with AMD 7 Series (and newer)

- Compatible with Altera Cyclone 10 devices (and newer)

- Compact

- Customizable

- Speed support from 1 Gbps to 100 Gbps

- Delivered as working reference design

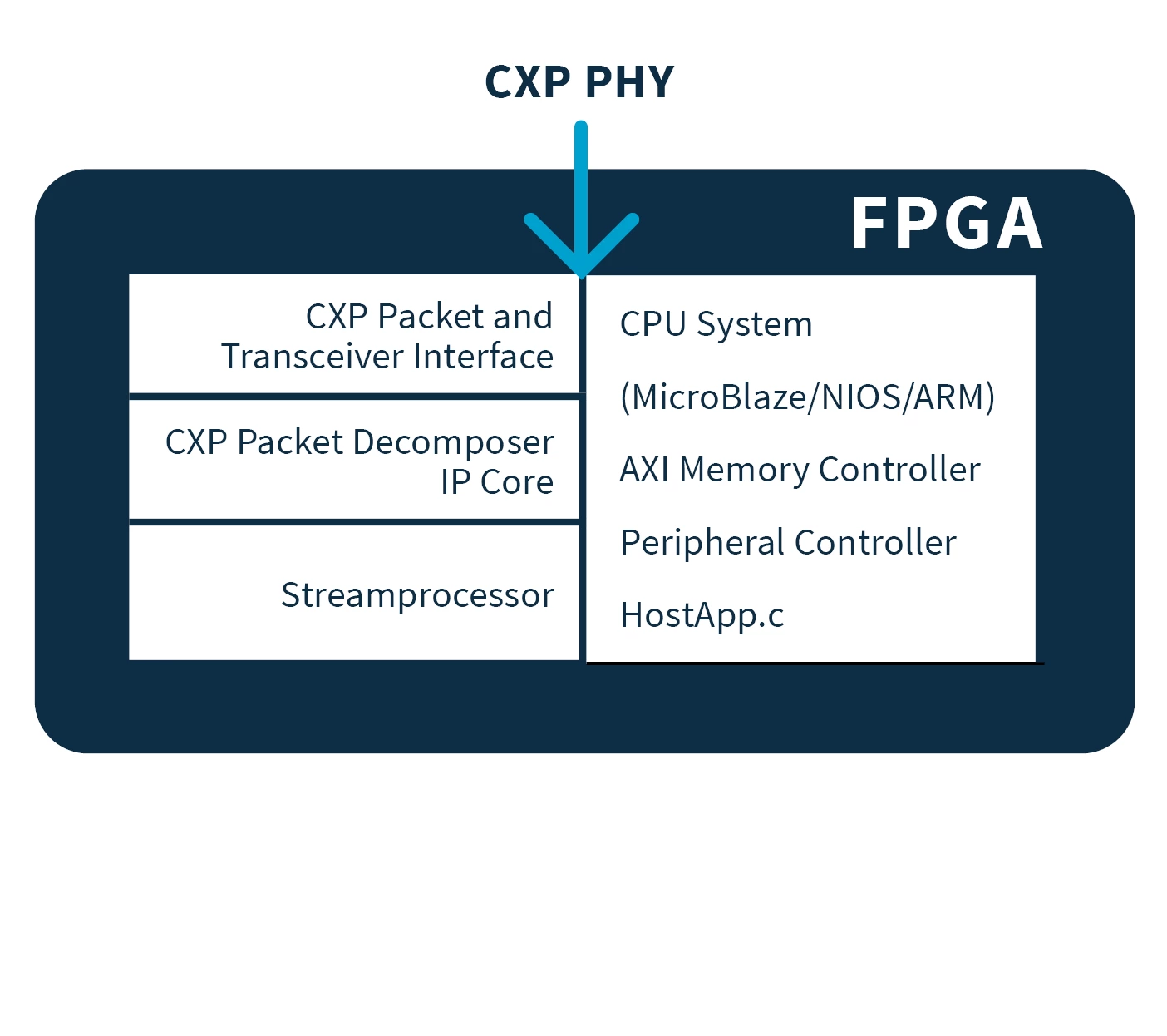

Architecture

CoaXPress (CXP) is a standard communication protocol for vision applications based on widely used coaxial cables. It allows easy interfacing between cameras and frame grabbers or embedded processors and supports the GenICam software standard. Sensor to Image offers a set of IP cores and a development framework to build FPGA-based receivers using the CoaXPress interface. Due to the speed of CXP, receivers require a fast FPGA-based implementation of the CXP core, using embedded transceivers. The CXP Host core is compatible with AMD and Altera devices.

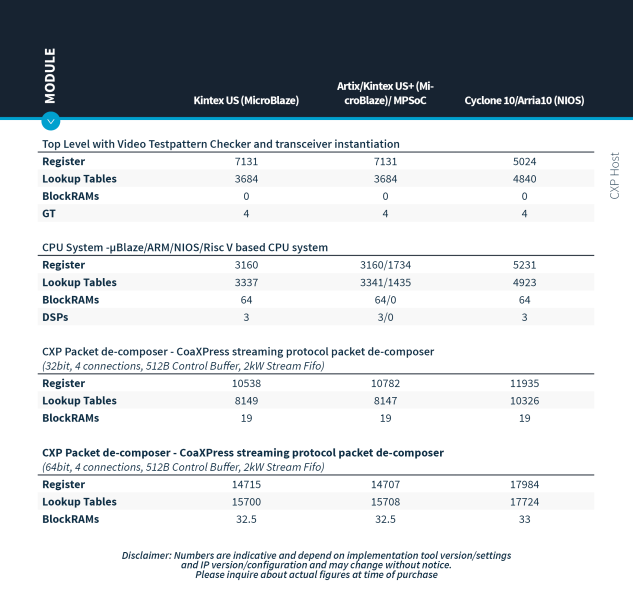

Resource Usage

Download resource usageBenefits

MVDK Machine Vision Development Kit For CoaXPress

Sensor to Image MVDK development kit is a flexible evaluation platform for machine vision applications. It supports CoaXPress host and device reference designs for various Enclustra FPGA modules with Altera and AMD FPGAs.

CoaXPress-Over-Fiber

A separate CoaXPress-over-Fiber Bridge IP Core is available to work with fiber cables, for longer distance, higher speed or in harsher environment.

Supplied Reference Design

Fully-functioning Reference Design: S2I’s FPGA solutions are delivered as a self-contained, fully-functioning reference design that is running on an agreed common platform along with FPGA IP Cores. This minimizes development time and allows for top-notch performance at a small footprint, while leaving enough flexibility to customize the design. Sensor to Image cores are compact and leave enough space in the FPGA for your application.

FPGA Integrated CPU

An FPGA integrated CPU (MicroBlaze, NIOS, ARM, Risc V) is used for several non-time-critical control and configuration tasks with the CXP-Device/Host core. This software is written in C and can be easily extended by the customer.

Top Level Design

The first component of the IP Core is the Top Level Design. It is an interface between external hardware (imager, sensors, CXP PHY) and FPGA internal data processing. We deliver this module as VHDL source code that can be adapted to custom hardware.

CXP Packet De-Composer

The CXP Control Interface sends and receives all data of the CXP control channel. The external CXP camera is controlled via this channel. The CXP Streaming Interface decodes all data from the camera and outputs them as an AXI stream. This stream can be used for further processing. The CXP Packet De Composer communicates with the CXP transport layer controller, which implements the high-speed interface to the FPGA transceivers. The IP Core is available with 32- or 64-bit wide datapaths for best resource – performance ratio. The 64-bit datapath makes the IP ready for CXP-25.

Stream Processing Module

As an example for video processing, the reference design comes with a simple display unit or a pattern checker module, that demonstrates the use of the video stream ouput of the CXP Packet De Composer unit.

FMC Interface Extensions

To extend the functionality of the various reference boards, we have designed FMC (FPGA Mezzanine Cards) that provide additional interfaces. We provide boards for CXP-6 and CXP-12 capable hardware with Microchip or Macom chipsets.