CoaXPress-Host-IP-Core

CoaXPress-Host-IP-Core für FPGA

- Kompatibel mit AMD 7 Series (und neuer)

- Kompatibel mit Altera Cyclone 10-Geräten (und neuer)

- Kompakt

- Anpassbar

- Geschwindigkeitsunterstützung von 1 Gbit/s bis 100 Gbit/s

- Lieferung als funktionsfähiges Referenzdesign

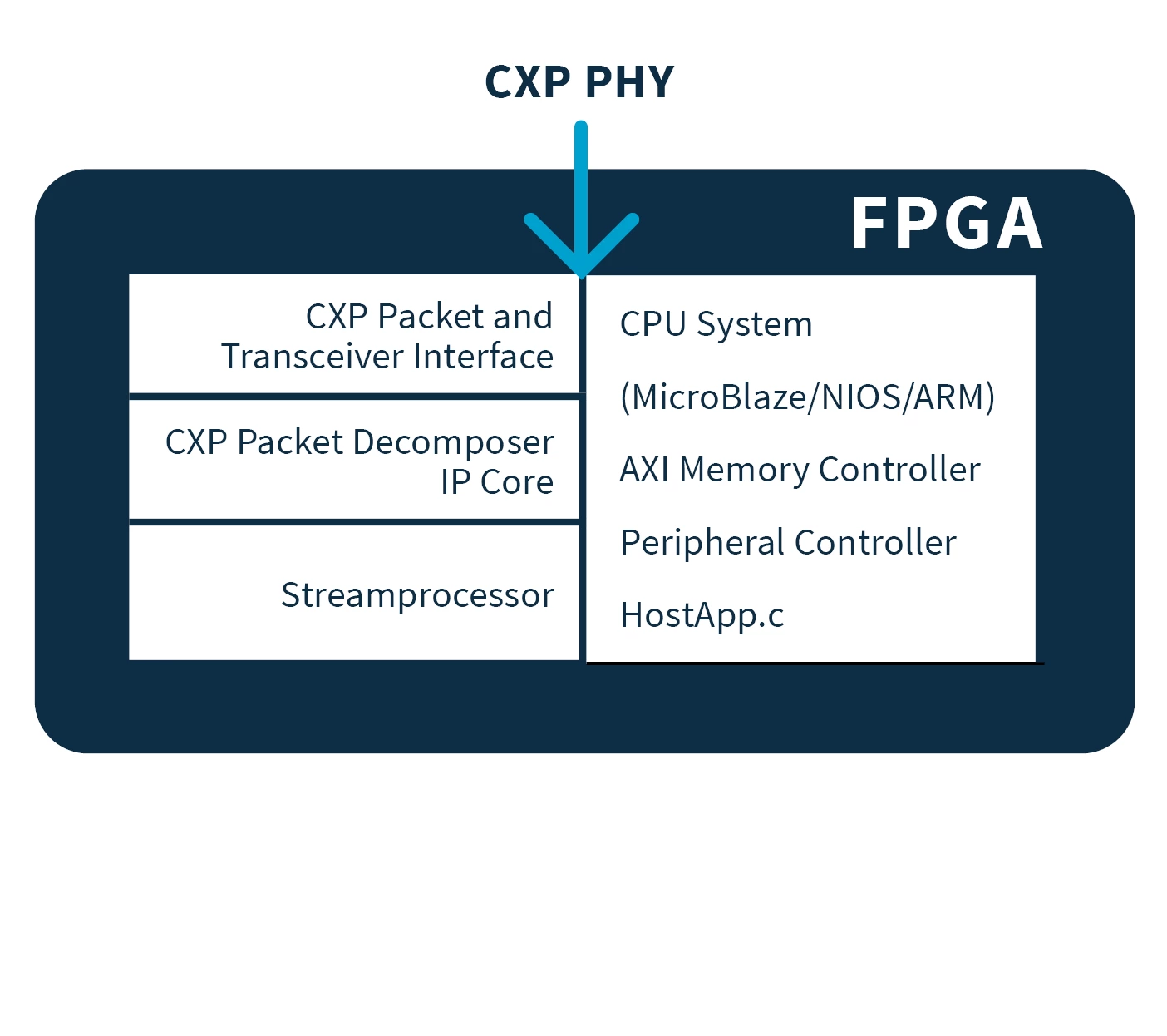

Architektur

CoaXPress (CXP) ist ein Standard-Kommunikationsprotokoll für Bildverarbeitungsanwendungen, das auf weit verbreiteten Koaxialkabeln basiert. Es ermöglicht eine einfache Verbindung zwischen Kameras und Framegrabbern oder eingebetteten Prozessoren und unterstützt den GenICam-Software-Standard. Sensor to Image bietet eine Reihe von IP Cores und ein Entwicklungsframework zum Aufbau von FPGA-basierten Empfängern unter Verwendung der CoaXPress-Schnittstelle. Aufgrund der Geschwindigkeit von CXP erfordern Empfänger eine schnelle FPGA-basierte Implementierung des CXP-Kerns unter Verwendung eingebetteter Transceiver. Der CXP-Host-Kern ist mit Geräten von AMD und Altera kompatibel.

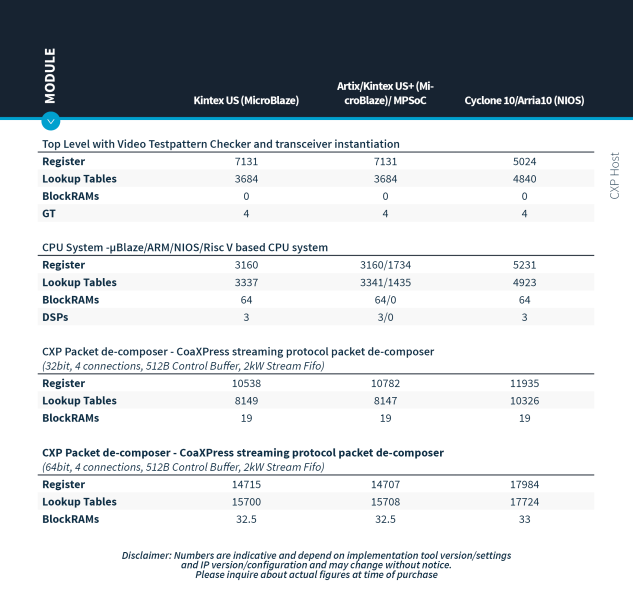

Ressourcenverbrauch

Ressourcenverbrauch herunterladenVorteile

MVDK Machine Vision Development Kit für CoaXPress

Das Sensor-to-Image-MVDK-Entwicklungskit ist eine flexible Evaluierungsplattform für Bildverarbeitungsanwendungen. Es unterstützt CoaXPress-Host- und Geräte-Referenzdesigns für verschiedene Enclustra-FPGA-Module mit Altera- und AMD-FPGAs.

CoaXPress über Glasfaser

Ein separater CoaXPress-over-Fiber-Bridge-IP-Core ist für den Einsatz mit Glasfaserkabeln verfügbar, um größere Entfernungen, höhere Geschwindigkeiten oder raue Umgebungsbedingungen zu bewältigen.

Mitgeliefertes Referenzdesign

Voll funktionsfähiges Referenzdesign: Die FPGA-Lösungen von S2I werden als eigenständiges, voll funktionsfähiges Referenzdesign geliefert, das auf einer vereinbarten gemeinsamen Plattform zusammen mit FPGA-IP Cores läuft. Dies minimiert die Entwicklungszeit und ermöglicht eine erstklassige Leistung bei geringem Platzbedarf, während gleichzeitig genügend Flexibilität für die Anpassung des Designs bleibt. Die Sensor-to-Image-Kerne sind kompakt und lassen genügend Platz im FPGA für Ihre Anwendung.

FPGA-integrierte CPU

Eine FPGA-integrierte CPU (MicroBlaze, NIOS, ARM, Risc V) wird für verschiedene nicht zeitkritische Steuerungs- und Konfigurationsaufgaben mit dem CXP-Device/Host-Kern verwendet. Diese Software ist in C geschrieben und kann vom Kunden leicht erweitert werden.

Top-Level-Design

Die erste Komponente des IP Cores ist das Top-Level-Design. Es handelt sich dabei um eine Schnittstelle zwischen externer Hardware (Imager, Sensoren, CXP PHY) und der internen Datenverarbeitung des FPGA. Wir liefern dieses Modul als VHDL-Quellcode, der an kundenspezifische Hardware angepasst werden kann.

CXP-Paket-Dekomponierer

Die CXP-Steuerschnittstelle sendet und empfängt alle Daten des CXP-Steuerkanals. Über diesen Kanal wird die externe CXP-Kamera gesteuert. Die CXP-Streaming-Schnittstelle decodiert alle Daten der Kamera und gibt sie als AXI-Stream aus. Dieser Stream kann zur weiteren Verarbeitung verwendet werden. Der CXP Packet De Composer kommuniziert mit dem CXP-Transportschicht-Controller, der die Hochgeschwindigkeitsschnittstelle zu den FPGA-Transceivern implementiert. Der IP Core ist mit 32- oder 64-Bit-Datenpfaden für ein optimales Verhältnis zwischen Ressourcen und Leistung erhältlich. Der 64-Bit-Datenpfad macht den IP Core bereit für CXP-25.

Stream-Verarbeitungsmodul

Als Beispiel für die Videoverarbeitung enthält das Referenzdesign eine einfache Anzeigeeinheit oder ein Musterprüfmodul, das die Verwendung des Videostream-Ausgangs der CXP Packet De Composer-Einheit demonstriert.

FMC-Schnittstellenerweiterungen

Um die Funktionalität der verschiedenen Referenzplatinen zu erweitern, haben wir FMC-Karten (FPGA Mezzanine Cards) entwickelt, die zusätzliche Schnittstellen bereitstellen. Wir bieten Platinen für CXP-6- und CXP-12-fähige Hardware mit Microchip- oder Macom-Chipsätzen an.