千兆网视觉主机 IP 核

千兆网Vision主机IP核用于FPGA

- 紧凑型

- 可定制

- 兼容AMD 7系列(及更新型号)和Altera Cyclone 10器件(及更新型号)

- 支持1 Gbps至10 Gbps以上的传输速率

- 以独立、功能完整的参考设计形式交付

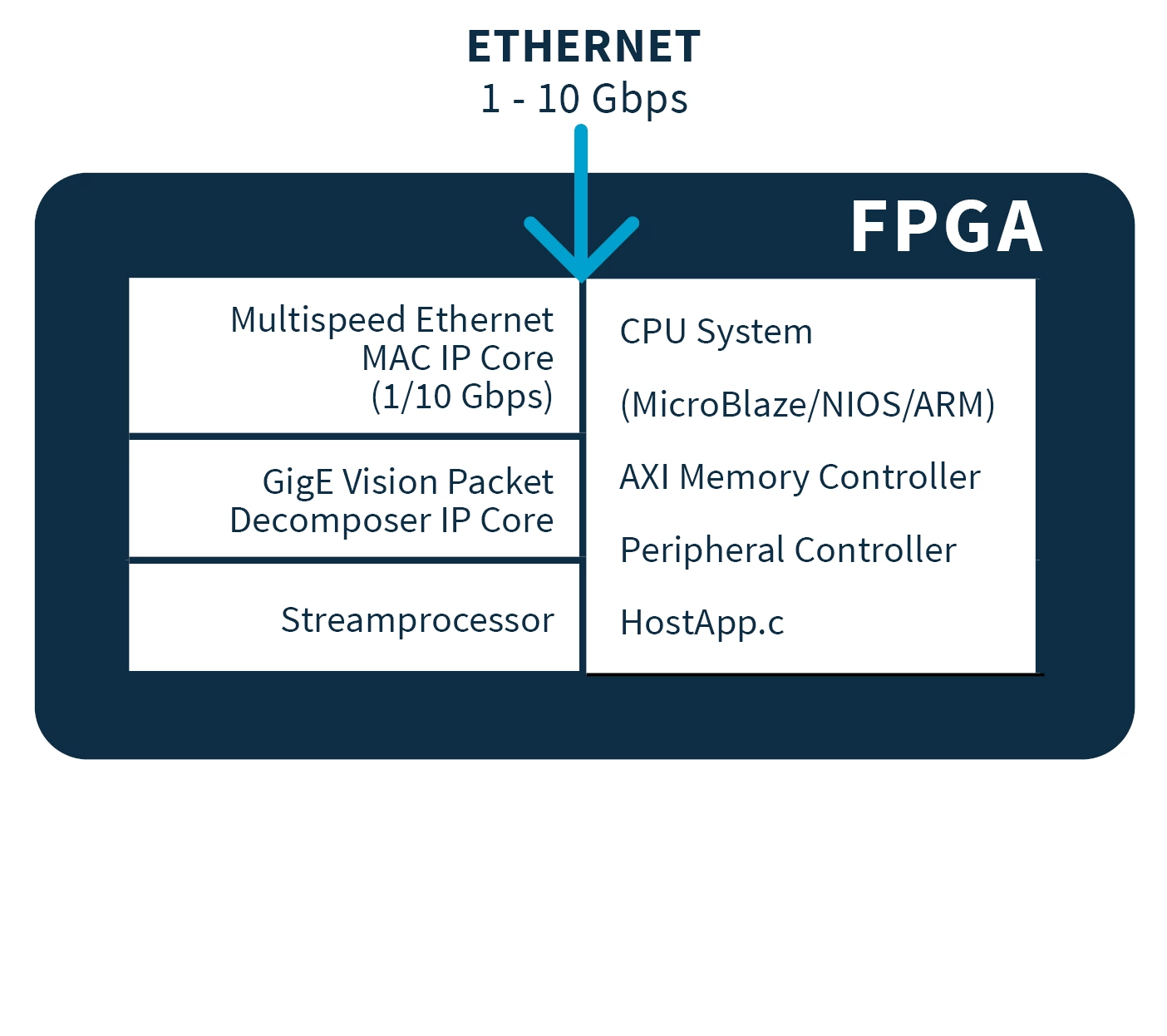

建筑

千兆网Vision是一种基于知名以太网技术的视觉应用标准通信协议。它能够轻松实现千兆网Vision设备与运行TCP/IP协议族的个人电脑之间的接口连接。 Sensor to Image 提供了一套 IP核与开发框架,用于基于千兆网 Vision 接口构建 FPGA 接收器产品。鉴于千兆网 Vision 的高速特性(尤其在超过 1 Gbps 的速率下),接收器需要采用基于 FPGA 的嵌入式千兆网 Vision 核高速实现方案。该千兆网 Vision 核套件兼容 AMD 和 Altera 器件。

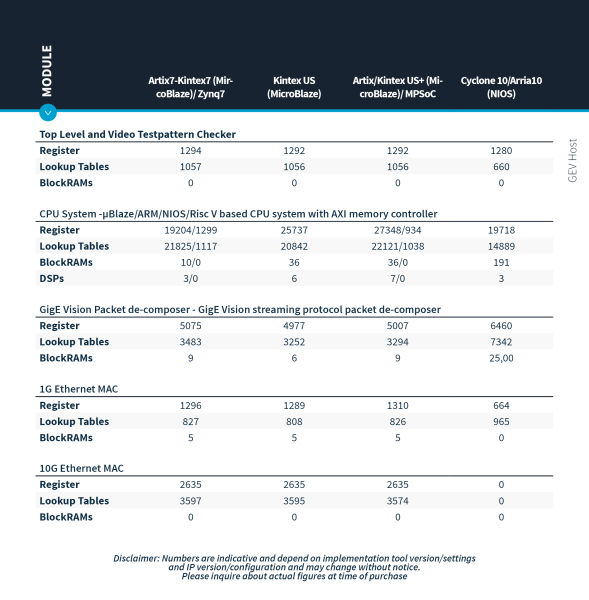

资源使用情况

下载资源使用情况福利

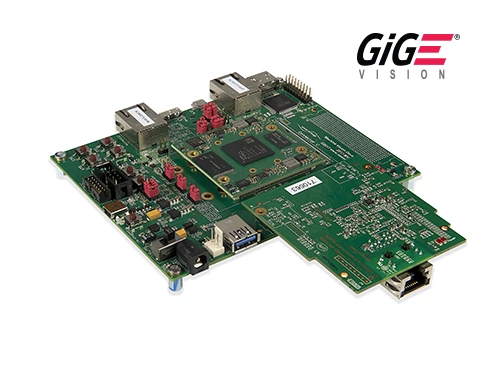

广泛支持FPGA开发套件

Sensor to Image的FPGA IP核以完全可运行的参考设计形式交付,搭载于FPGA开发套件中。我们支持AMD、Altera和Microchip等厂商的多种现成套件。

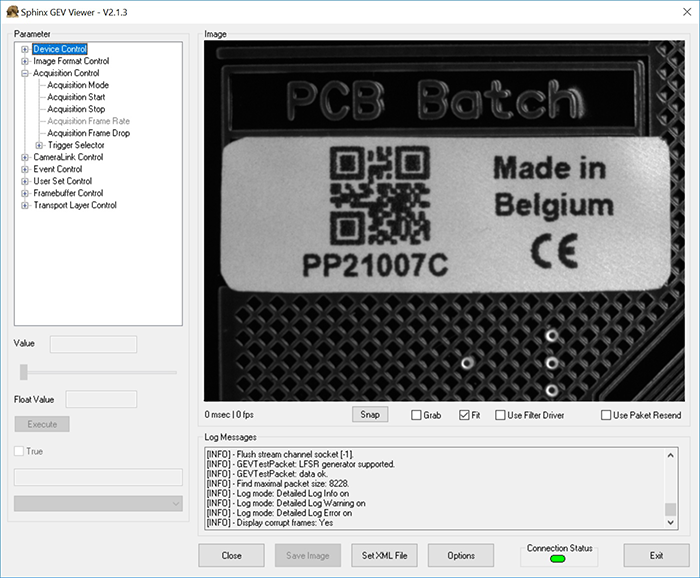

包含Sphinx SDK

功能丰富的软件工具包,提供构建模块,可快速轻松地设计高性能视频应用程序,同时最大限度降低CPU资源消耗。该工具包还包含适用于Windows或Linux的滤镜驱动程序和采集库,以及示例应用程序,包括符合千兆网Vision/GenICam标准的查看器。

多流支持

千兆网Vision主机IP具备通过单一链路接收多个数据流的能力。此功能可用于从多台相机采集图像数据。请注意,在此应用场景下强烈建议在嵌入式CPU上运行Linux系统。

提供的参考设计

功能完备的参考设计:S2I的FPGA解决方案以独立、功能完备的参考设计形式交付,该设计在约定通用平台上运行,并集成FPGA IP核。此方案可最大限度缩短开发周期,在小尺寸封装下实现顶尖性能,同时保留充足的定制灵活性。传感器到图像核结构紧凑,为您的应用在FPGA中预留充足空间。

顶层设计

IP核的首个组件是顶层设计。它作为外部硬件(成像器、传感器、千兆网物理层)与FPGA内部数据处理之间的接口。我们以VHDL源代码形式交付该模块,可适配定制硬件。

C语言软件库源代码

GigE Vision IP核的嵌入式GigE Vision库可选择以源代码形式交付。此功能有助于扩展功能,以支持不常用的GigE Vision可选特性,或更精准地匹配硬件需求。通过额外驱动程序,可在设备上实现Linux操作系统的使用。

千兆网数据包分解器

千兆网数据包分解器从数据包流中提取视频和控制数据。该设备将所有千兆网Vision控制数据发送至CPU系统,并将千兆网Vision流式数据以AXI流形式输出。

斯芬克斯千兆网视觉服务器

交付内容包含Sphinx千兆网Vision Server,这是一款软件相机模拟器。该服务器有助于快速熟悉设计流程,并展示如何与第三方相机进行通信。

流处理模块

作为视频处理的示例,该参考设计配备了一个简单的显示单元或图案检测模块,用于演示千兆网数据包分解器单元视频流输出的应用场景。

FPGA集成CPU

采用FPGA集成CPU设计(MicroBlaze、NIOS、ARM、Risc V)处理若干非实时性网络及配置任务,同时实现千兆网Vision控制协议(GVCP)。该软件采用C语言编写,支持客户扩展功能。

FMC接口扩展

为扩展各类参考板的功能,我们提供支持1G以太网和10G以太网(含NBaseT技术)的FMC扩展卡。