# eGrabber

## FrameGrabbers Handbook

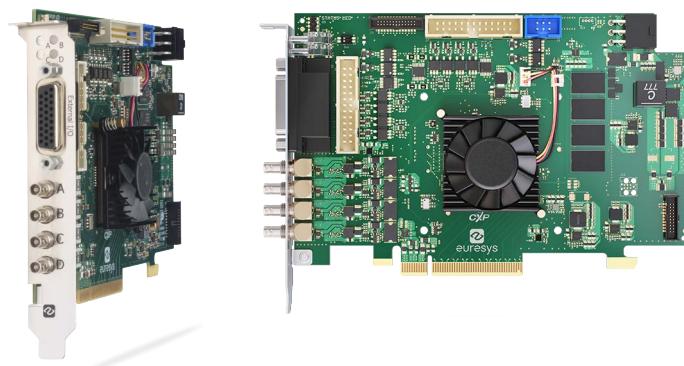

28768 | PC1633-T Coaxlink Quad G3

28776 | PC3602-T Coaxlink Octo

28781 | PC3621-LH-T Coaxlink Mono CXP-12-LH

28782 | PC3622-T Coaxlink Duo CXP-12

28783 | PC3623-T Coaxlink Quad CXP-12 Value

# Contact us

## Website, email

### General

[www.alliedvision.com/en/contact](http://www.alliedvision.com/en/contact)

[info@alliedvision.com](mailto:info@alliedvision.com)

### Distribution partners

[www.alliedvision.com/en/avt-locations/avt-distributors](http://www.alliedvision.com/en/avt-locations/avt-distributors)

### Support

[www.alliedvision.com/en/support](http://www.alliedvision.com/en/support)

[www.alliedvision.com/en/about-us/contact-us/technical-support-repair-/rma](http://www.alliedvision.com/en/about-us/contact-us/technical-support-repair-/rma)

## Offices

### Europe, Middle East, and Africa (Headquarters)

Allied Vision Technologies GmbH

Taschenweg 2a

07646 Stadtroda, Germany

T// +49 36428 677-0 (Reception)

T// +49 36428 677-230 (Sales)

F// +49 36428 677-28

### Asia-Pacific | China

Allied Vision Technologies Shanghai Co Ltd.

B-510, Venture International Business Park

2679 Hechuan Road

Minhang District, Shanghai 201103

People's Republic of China

T// +86 21 64861133

### Singapore

Allied Vision Technologies Asia Pte. Ltd

82 Playfair Rd, #07-01 D'Lithium

Singapore 368001

T// +65 6634 9027

### North, Central, and South America, Canada

Allied Vision Technologies Canada Inc.

300 – 4621 Canada Way

Burnaby, BC V5G 4X8, Canada

T// +1 604 875 8855

### USA

Allied Vision Technologies, Inc.

102 Pickering Way - Suite 502

Exton, PA 19341, USA

Toll-free// +1-877-USA-1394

T// +1 978 225 2030

### Japan

Allied Vision Technologies

Yokohama Portside Bldg. 10F

8-1 Sakae-cho, Kanagawa-ku

Yokohama-shi, Kanagawa, 221-0052

T// +81 (0) 45 577 9527

This documentation is provided with **eGrabber 25.07.1** (doc build 2202).

<https://www.alliedvision.com>

This documentation is subject to the General Terms and Conditions stated on the website of **Allied Vision Technologies GmbH** and available on <https://www.alliedvision.com/en/information/terms-conditions/>.

# Contents

|                                                   |    |

|---------------------------------------------------|----|

| <b>PART I : GETTING STARTED</b>                   | 8  |

| 1. Hardware Setup                                 | 9  |

| 1.1. Precautions for Use of Board Products        | 9  |

| 1.2. PCI Express Card Slot Requirements           | 10 |

| 1.3. PCI Express Card Installation Procedure      | 11 |

| 1.4. Low-Profile Bracket Installation             | 11 |

| 2. Software Setup                                 | 12 |

| 2.1. Software Setup Procedure                     | 12 |

| 2.2. Important Notices                            | 12 |

| Firmware Revisions                                | 12 |

| CPU Requirements                                  | 13 |

| Image Buffer Limits                               | 13 |

| Notice for Windows                                | 13 |

| Notice for Linux                                  | 14 |

| Notice for NVIDIA RDMA                            | 14 |

| Notices for macOS                                 | 15 |

| 2.3. Installing eGrabber                          | 16 |

| Installing eGrabber on Windows                    | 16 |

| Installing eGrabber on Linux                      | 17 |

| Installing eGrabber on macOS                      | 17 |

| Command-Line Installation Procedure               | 19 |

| 3. Managing Firmware                              | 20 |

| 3.1. What's Firmware?                             | 21 |

| 3.2. Firmware Manager Tools                       | 22 |

| 3.3. Updating and Installing Firmware             | 24 |

| 3.4. Firmware Recovery Switch                     | 25 |

| 4. Firmware Variants                              | 26 |

| <b>PART II : FUNCTIONAL GUIDE</b>                 | 29 |

| 1. Architecture of eGrabber-driven frame grabbers | 30 |

| 1.1. Main Elements                                | 31 |

| 1.2. Block Diagrams                               | 33 |

| 2. CoaXPress Host Interface                       | 37 |

| 2.1. CoaXPress Interface Specifications           | 38 |

| 2.2. Host Connections Maps for Coaxlink Series    | 41 |

| 2.3. CoaXPress Link Configuration                 | 51 |

| 2.4. Power Over CoaXPress                         | 52 |

| 2.5. CoaXPress I/O Channel                        | 55 |

| 2.6. CoaXPress Host To Device Trigger             | 56 |

| 2.7. Advanced Trigger Transmitter Settings        | 58 |

| 2.8. Camera Trigger Jitter Compensation           | 60 |

| 2.9. Trigger Delay Model                          | 63 |

| 2.10. CoaXPress LED Lamps                         | 66 |

| 2.11. Connection Test                             | 68 |

| 2.12. CoaXPress 2.0 Error Counters                | 69 |

| 2.13. CoaXPress Link Validation Tool              | 71 |

| 2.14. Multi-tap CoaXPress Cameras                 | 77 |

| 3. On-board Memory                                | 78 |

| 3.1. Partition Schemes                            | 79 |

|                                                                    |     |

|--------------------------------------------------------------------|-----|

| 4. Acquisition Gate .....                                          | 87  |

| 5. Area-scan Acquisition .....                                     | 88  |

| 5.1. Area-scan Acquisition Principles .....                        | 89  |

| 5.2. High Frame Rate Acquisition .....                             | 90  |

| 5.3. Multi-Stream Acquisition .....                                | 92  |

| 6. Line-scan Acquisition .....                                     | 93  |

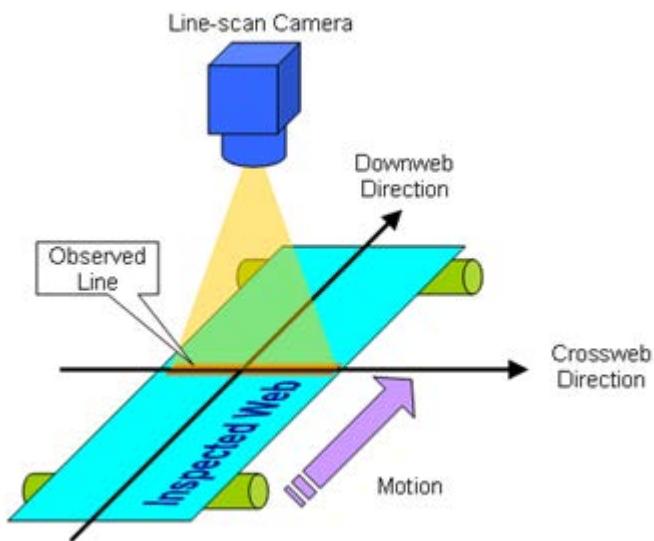

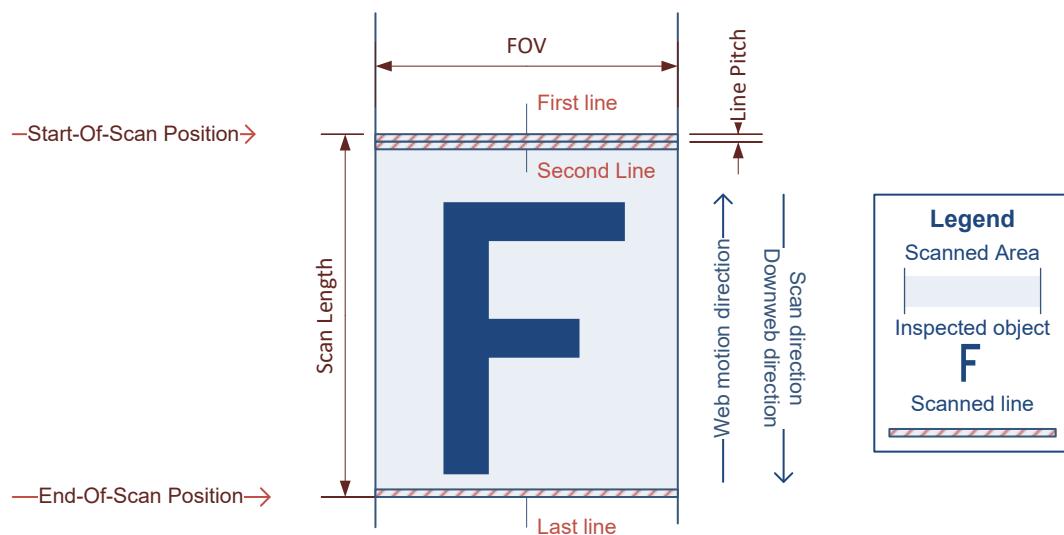

| 6.1. Line-scan Acquisition Principles .....                        | 94  |

| 6.2. Line-scan Acquisition Use cases .....                         | 98  |

| 6.3. Metadata Insertion .....                                      | 102 |

| 6.4. Trigger to Line Latency Compensation .....                    | 106 |

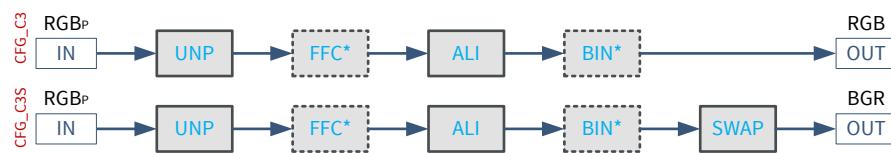

| 7. Pixel Processing .....                                          | 107 |

| 7.1. Overview .....                                                | 107 |

| 7.2. Configurations .....                                          | 110 |

| 7.3. Pixel Unpacking and Alignment .....                           | 118 |

| 7.4. Flat Field Correction .....                                   | 120 |

| What is Flat Field Correction? .....                               | 121 |

| FFC IP Core Description .....                                      | 124 |

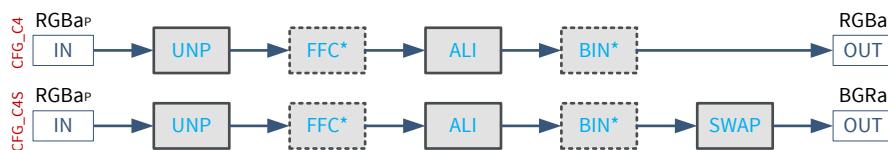

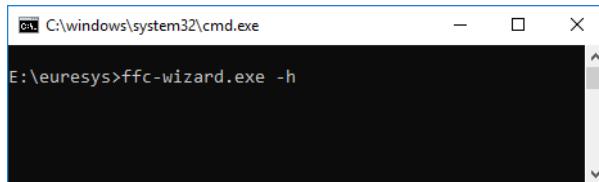

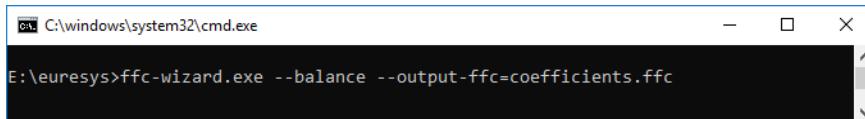

| FFC Wizard Sample Program .....                                    | 127 |

| 7.5. Lookup Table Processing .....                                 | 133 |

| Introduction to LUT Processing .....                               | 134 |

| Monochrome Lookup Table Processing .....                           | 135 |

| LUT Content Definition .....                                       | 136 |

| LUT Setup Procedure .....                                          | 143 |

| 7.6. Bayer CFA Decoding .....                                      | 146 |

| Bayer CFA Decoding Methods .....                                   | 147 |

| Requirements and Performances .....                                | 149 |

| Using Bayer CFA Decoder .....                                      | 151 |

| Advanced and Legacy Methods .....                                  | 153 |

| 7.7. Pixel Binning .....                                           | 157 |

| Binning Configurations .....                                       | 158 |

| Specifications .....                                               | 160 |

| Limitations .....                                                  | 161 |

| 7.8. Pixel Components Swapping .....                               | 163 |

| 7.9. Endianness Conversion .....                                   | 164 |

| 7.10. Pixel Ordering .....                                         | 165 |

| 8. Image Data Transfer .....                                       | 166 |

| 8.1. Buffer Filling Rules .....                                    | 167 |

| 8.2. Image Width Increment Step .....                              | 169 |

| 8.3. Image Data Padding .....                                      | 171 |

| 8.4. Horizontal Image Flipping .....                               | 173 |

| 8.5. Vertical Image Flipping .....                                 | 174 |

| 8.6. Image Data Unscrambling .....                                 | 175 |

| 8.7. Transmission Methods of 1X_2YE Images (Coaxlink series) ..... | 180 |

| 8.8. Data Stream Statistics .....                                  | 182 |

| 8.9. Data Transfer Rate Test Program .....                         | 184 |

| 9. Camera and Illumination Control .....                           | 187 |

| 9.1. Camera Control Principles .....                               | 188 |

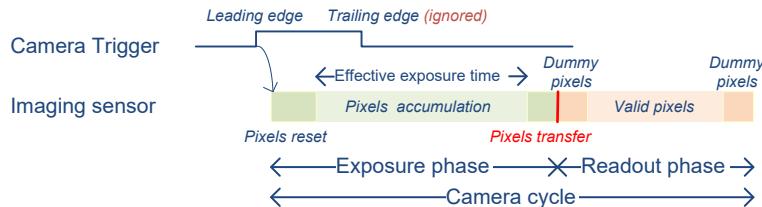

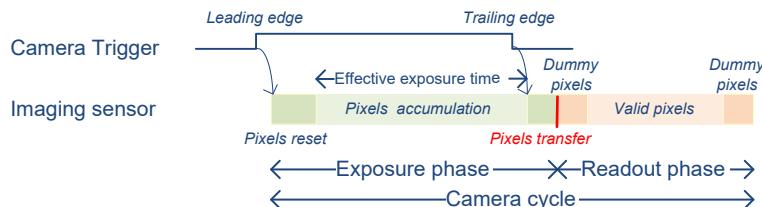

| Camera Cycle .....                                                 | 189 |

| Camera Cycle Concatenation Rules .....                             | 190 |

| Camera Control Methods .....                                       | 192 |

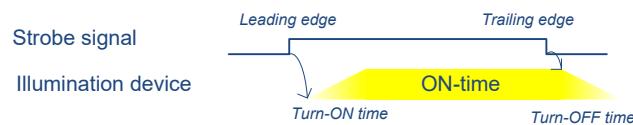

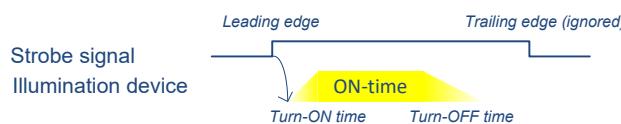

| 9.2. Illumination Control Principles .....                         | 195 |

| Illumination Devices .....                                         | 196 |

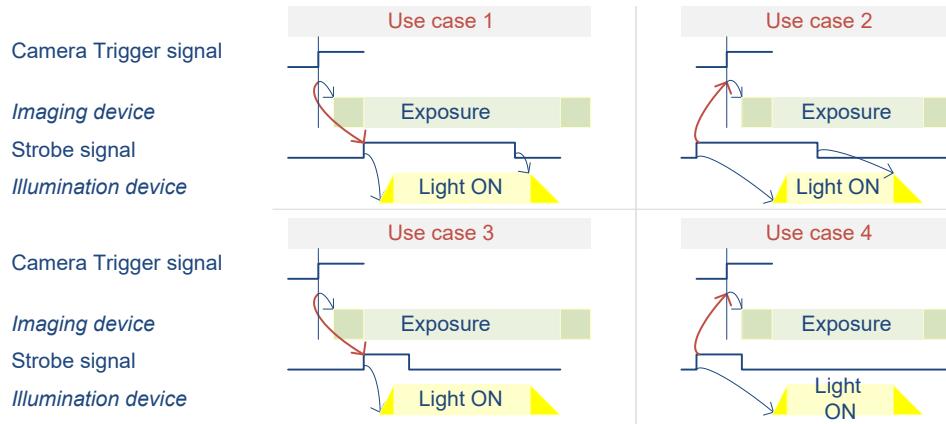

| Aligning Camera and Illumination Cycles .....                      | 197 |

| 9.3. Camera and Illumination Controller .....                      | 198 |

| Camera and Illumination Controller Overview .....                  | 198 |

|                                                 |     |

|-------------------------------------------------|-----|

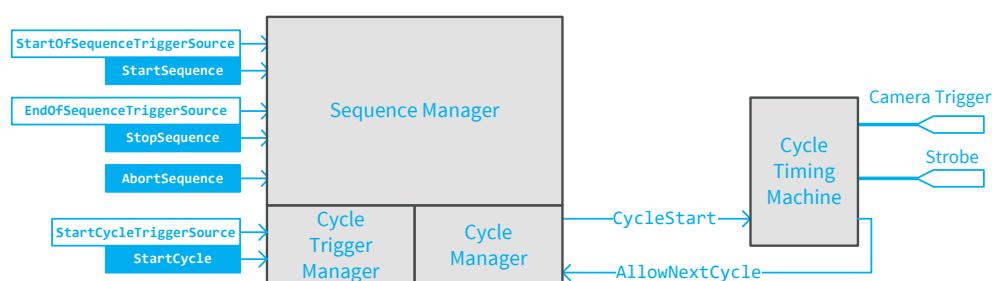

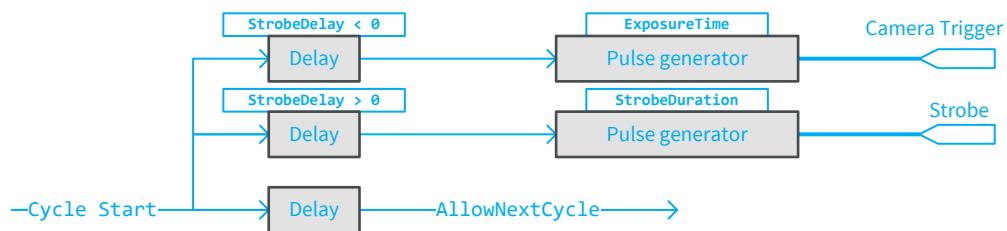

| Cycle Timing Machine .....                      | 199 |

| Multiple Cycle Timings .....                    | 201 |

| Cycle Manager .....                             | 202 |

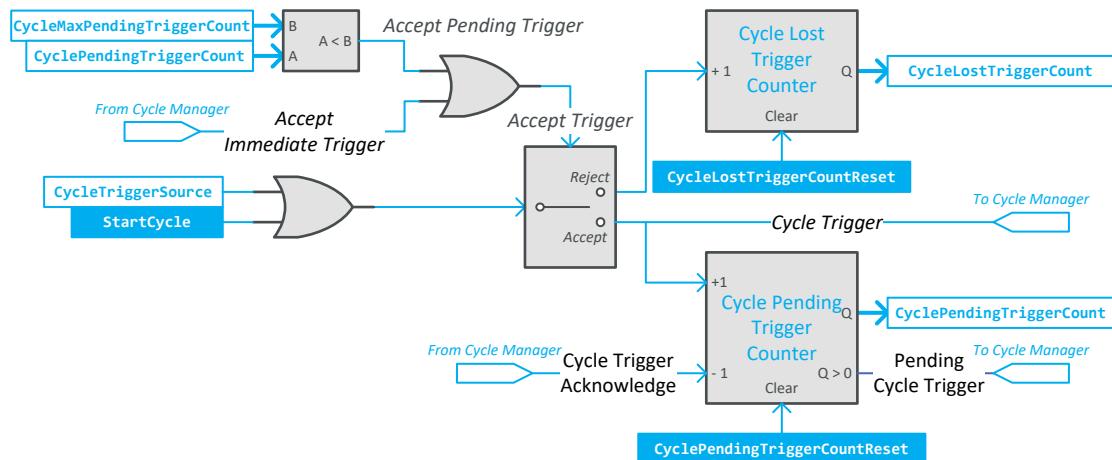

| Cycle Trigger Manager .....                     | 203 |

| Sequence Manager .....                          | 205 |

| CIC Output Signals Routing .....                | 207 |

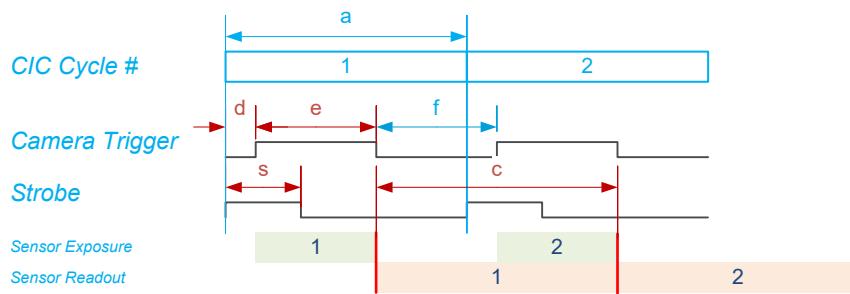

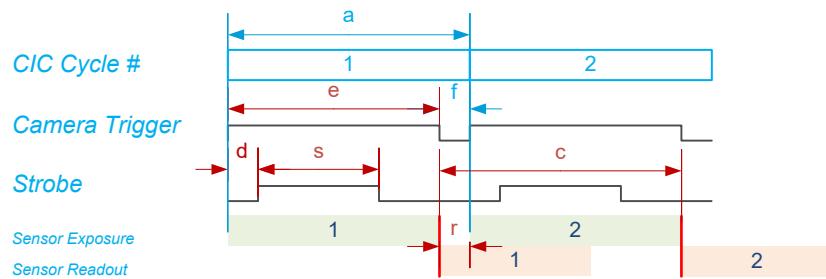

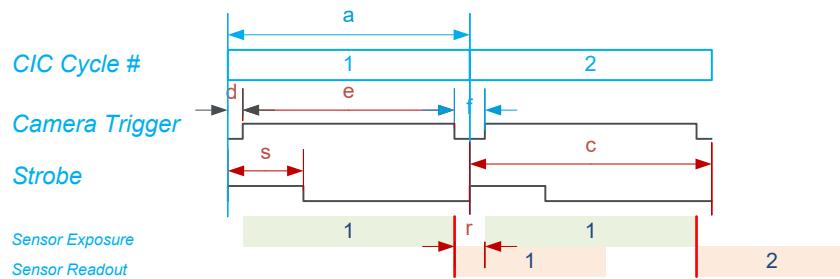

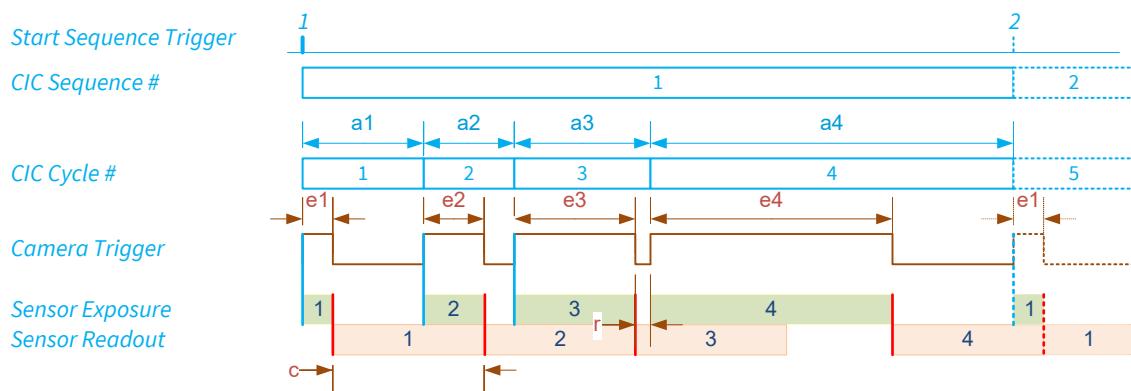

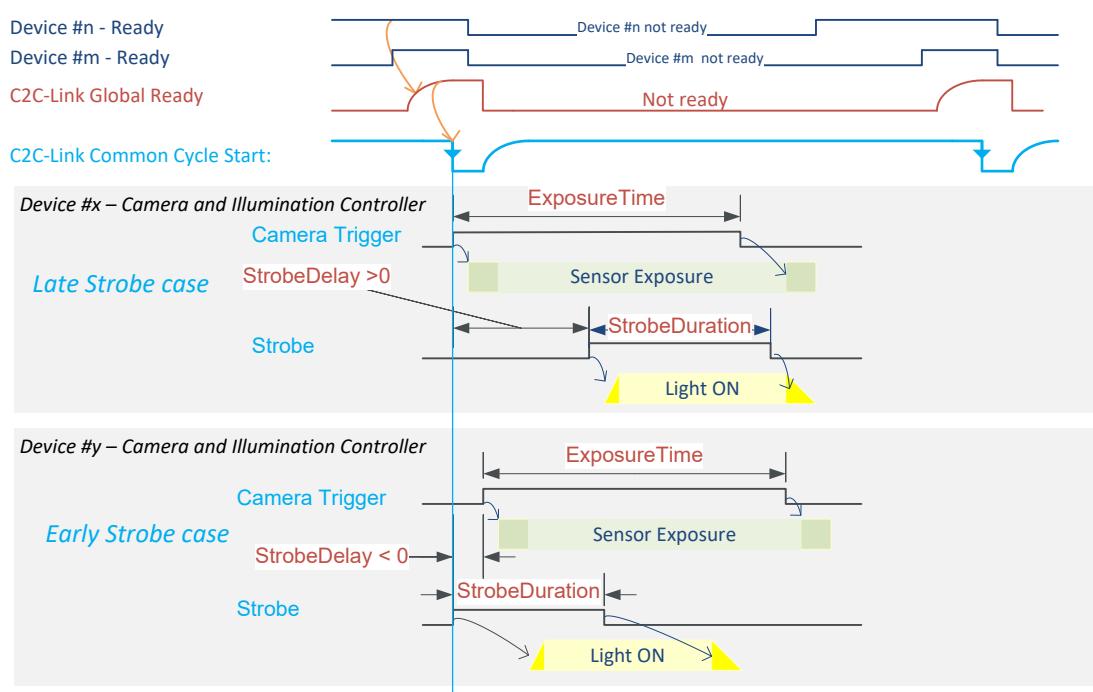

| 9.4. CIC Timing Diagrams .....                  | 208 |

| Single Cycle .....                              | 209 |

| Overlapping Cycles - Single timing .....        | 211 |

| Multiple Timings Example .....                  | 216 |

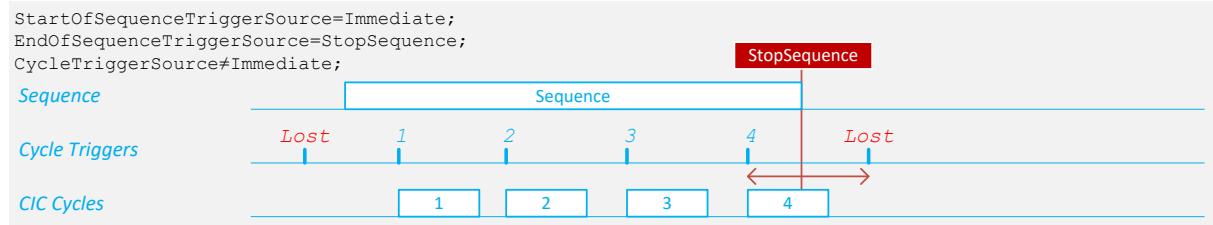

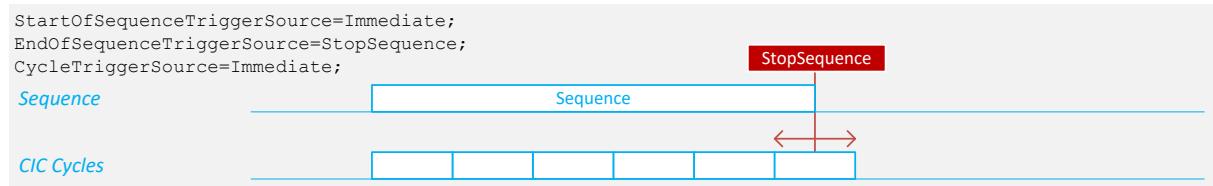

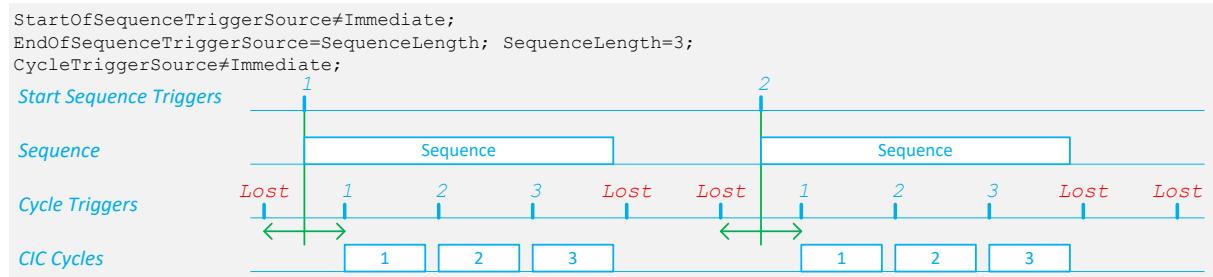

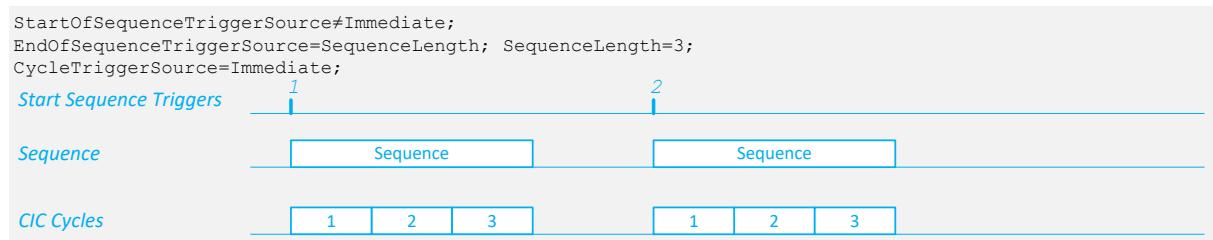

| Cycle Sequence Timing Diagrams .....            | 218 |

| 10. General Purpose I/O .....                   | 220 |

| 10.1. I/O Lines Overview .....                  | 221 |

| 10.2. I/O Lines Usage .....                     | 224 |

| 10.3. I/O Control Blocks .....                  | 225 |

| 10.4. Line Format and Line Mode Controls .....  | 227 |

| 10.5. Line Polarity Control .....               | 230 |

| 10.6. Line Filter Control .....                 | 231 |

| 10.7. Line Source Selection .....               | 232 |

| 10.8. Line Source Divider .....                 | 233 |

| 10.9. Logical I/O Line State .....              | 234 |

| 10.10. Physical I/O Line State .....            | 235 |

| 10.11. Line Driver Physical Output States ..... | 236 |

| 10.12. Initial States .....                     | 237 |

| 11. I/O Toolbox .....                           | 238 |

| 11.1. Introducing the I/O Toolbox .....         | 239 |

| 11.2. I/O Toolbox Composition Tables .....      | 241 |

| 11.3. Line Input Tool .....                     | 244 |

| 11.4. Quadrature Decoder Tool .....             | 245 |

| 11.5. Device Link Trigger Tool .....            | 248 |

| 11.6. User Actions Tool .....                   | 249 |

| 11.7. C2C-Link Synchronization Tool .....       | 254 |

| 11.8. Delay Tool .....                          | 256 |

| 11.9. Divider Tool .....                        | 258 |

| 11.10. Multiplier/Divider Tool .....            | 259 |

| 12. Event Signaling And Counting .....          | 262 |

| 12.1. Introduction .....                        | 263 |

| 12.2. Custom Event Sources .....                | 266 |

| EVENT_CUSTOM_CIC .....                          | 267 |

| EVENT_CUSTOM_CXP_DEVICE .....                   | 268 |

| EVENT_CUSTOM_CXP_INTERFACE .....                | 268 |

| EVENT_CUSTOM_DATASTREAM .....                   | 270 |

| EVENT_CUSTOM_DEVICE_ERROR .....                 | 271 |

| EVENT_CUSTOM_IO_TOOLBOX .....                   | 272 |

| 12.3. Event Specific Context Data .....         | 274 |

| 12.4. About GenTL Signaling .....               | 276 |

| 13. Advanced Features .....                     | 277 |

| 13.1. C2C-Link .....                            | 278 |

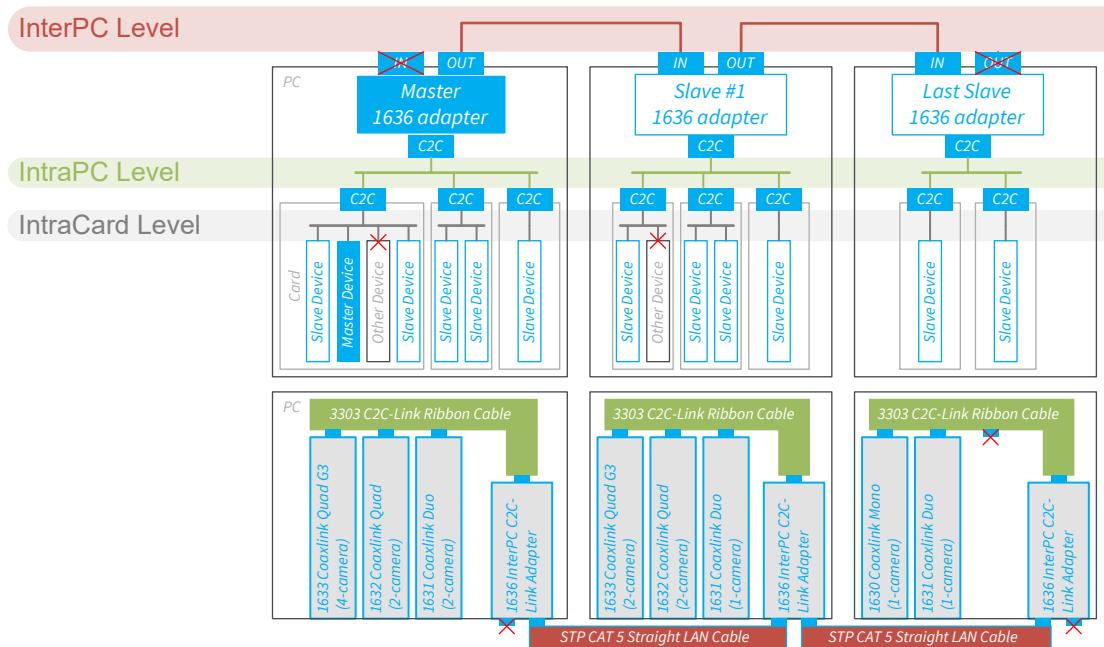

| C2C-Link Interconnections .....                 | 279 |

| C2C-Link Electrical Specification .....         | 280 |

| Trigger Propagation Delays .....                | 282 |

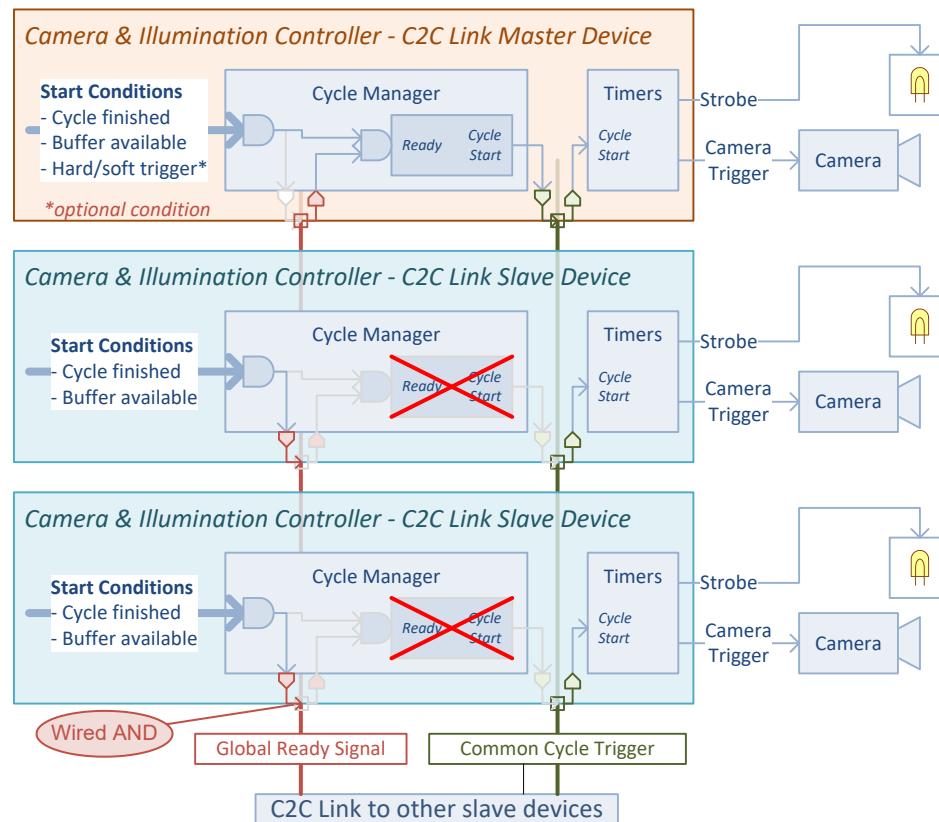

| Cycle Trigger Synchronization .....             | 284 |

| C2C-Link Setup Procedure .....                  | 287 |

| 13.2. OEM Safety Key .....                      | 289 |

| Introducing OEM Safety Key .....                | 290 |

|                                                          |            |

|----------------------------------------------------------|------------|

| Using OEMSafetyKey .....                                 | 291        |

| <b>PART III : HARDWARE MANUAL .....</b>                  | <b>292</b> |

| 1. Mechanical Specification .....                        | 293        |

| 1.1. Product Layouts .....                               | 294        |

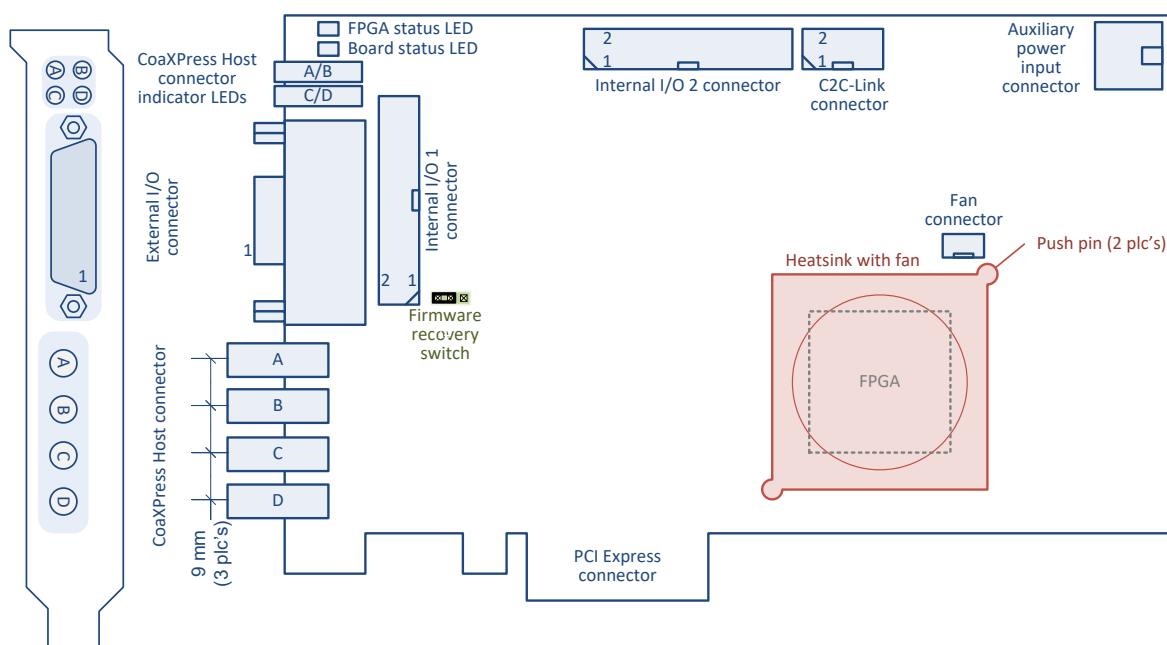

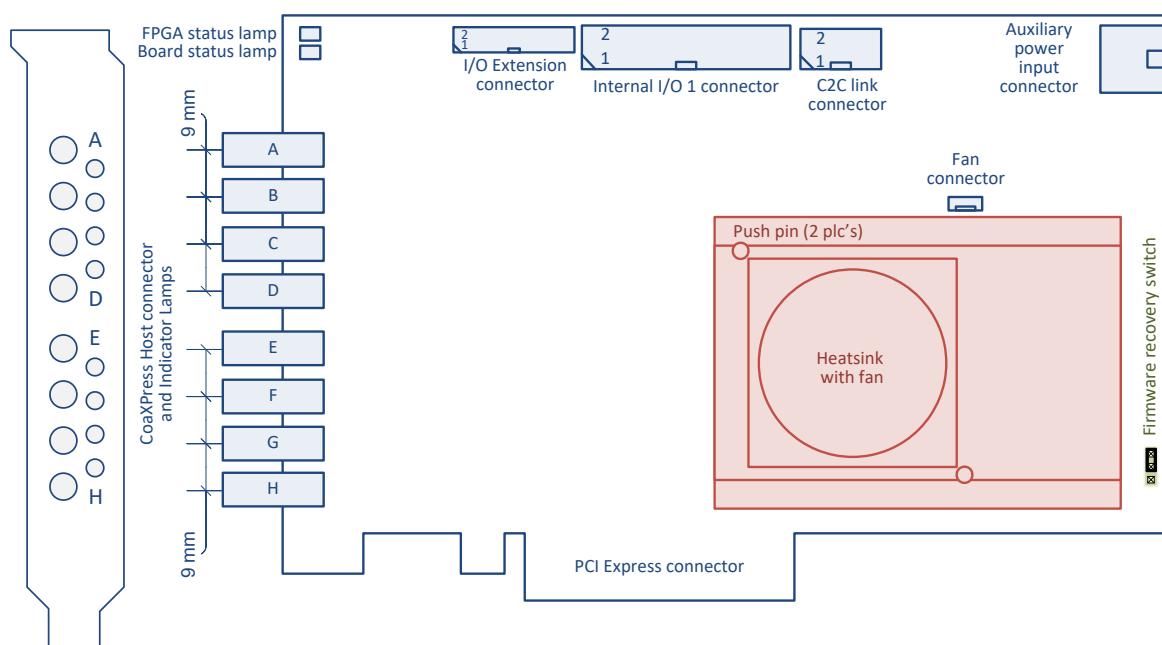

| PC1633-T Coaxlink Quad G3 .....                          | 295        |

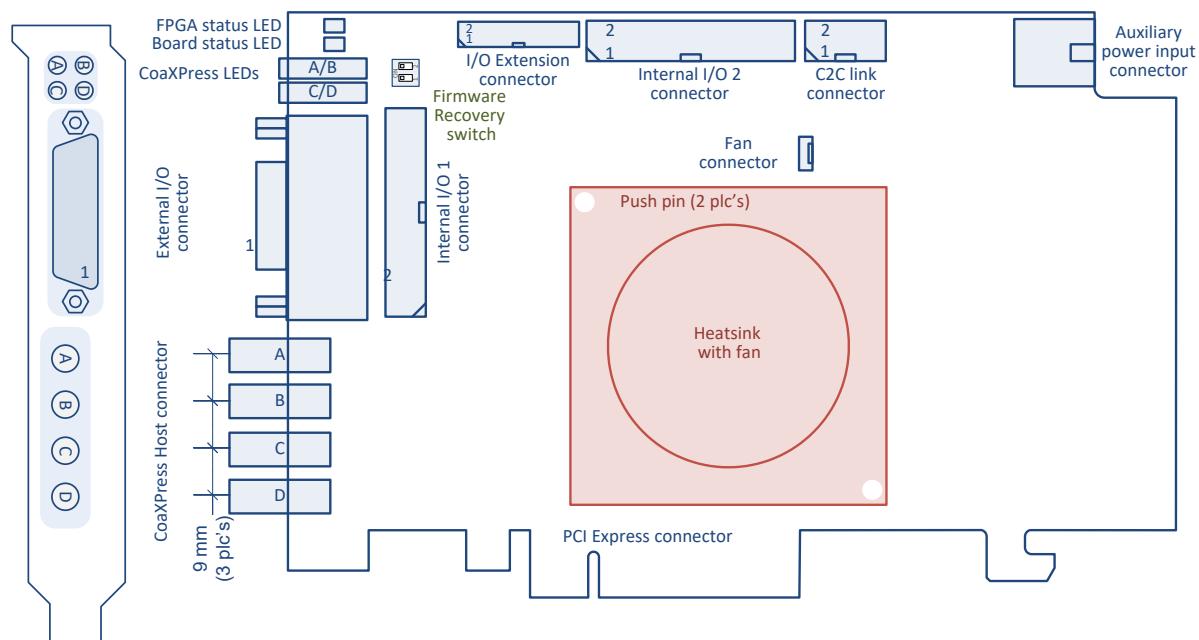

| PC3602-T Coaxlink Octo .....                             | 296        |

| PC3621-LH-T Coaxlink Mono CXP-12-LH .....                | 297        |

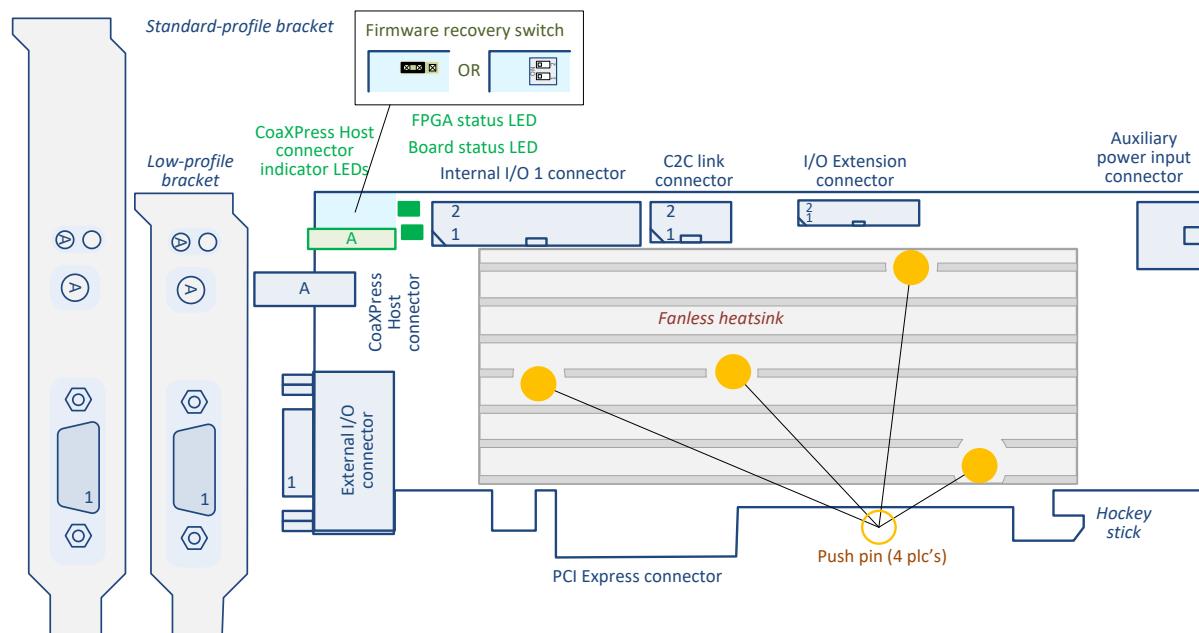

| PC3622-T Coaxlink Duo CXP-12 .....                       | 298        |

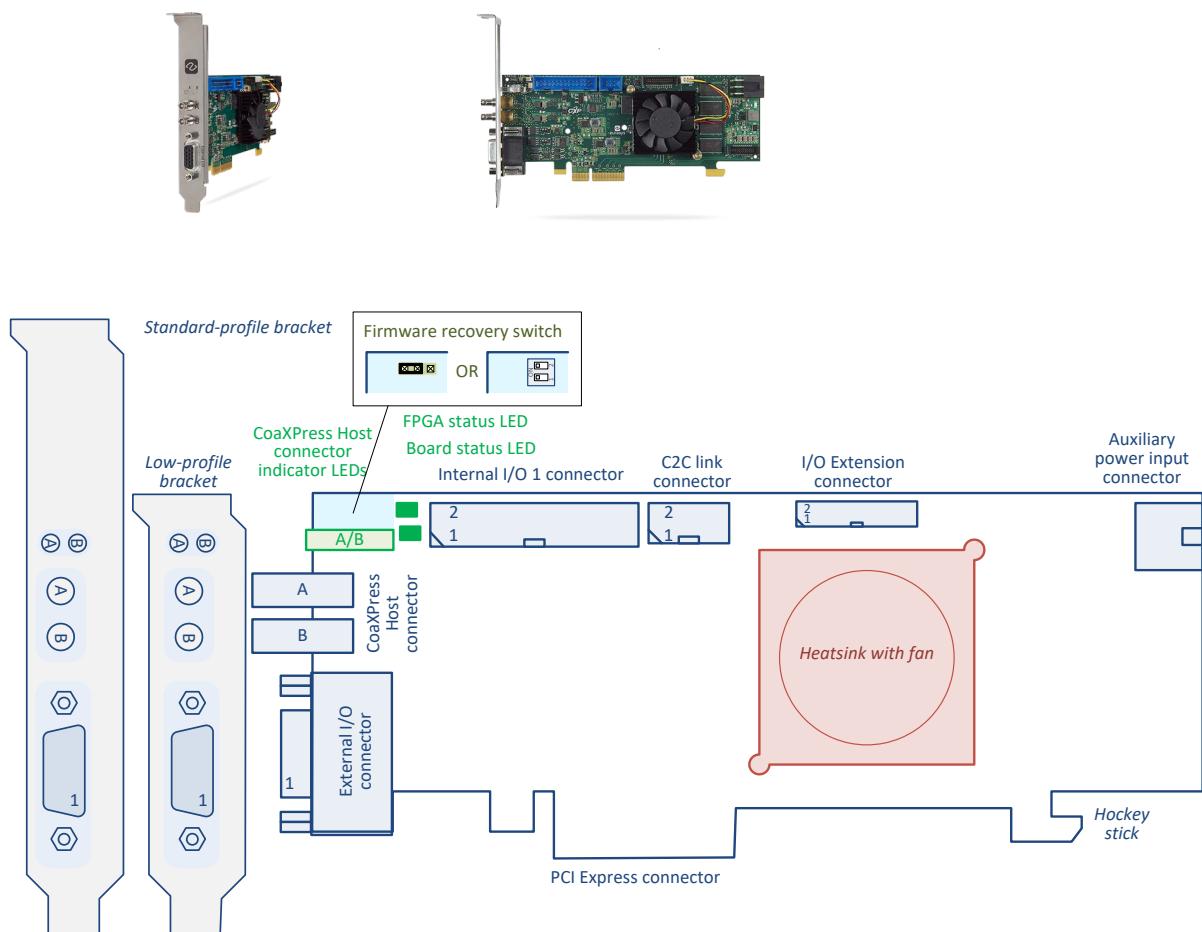

| PC3623-T Coaxlink Quad CXP-12 Value .....                | 299        |

| 1.2. Camera and Data Output Connectors .....             | 300        |

| CoaXPress DIN 4 Connector .....                          | 301        |

| CoaXPress DIN 8 Connector .....                          | 302        |

| CoaXPress Micro-BNC 1 Connector .....                    | 303        |

| CoaXPress Micro-BNC 2 Connector .....                    | 304        |

| CoaXPress Micro-BNC 4 Connector .....                    | 305        |

| 1.3. GPIO Connectors .....                               | 306        |

| External I/O Connector .....                             | 307        |

| External I/O 15-pin Connector .....                      | 309        |

| Internal I/O 1 Connector .....                           | 310        |

| Internal I/O 2 Connector .....                           | 312        |

| 1.4. Other Connectors .....                              | 314        |

| I/O Extension Connector .....                            | 315        |

| C2C-Link Connector .....                                 | 317        |

| Auxiliary Power Input Connector for PoCXP and GPIO ..... | 318        |

| Auxiliary Power Input Connector w/o SenseIN .....        | 319        |

| 1.5. LEDs and Switches .....                             | 320        |

| CoaXPress LED Lamps .....                                | 321        |

| Board Status LED .....                                   | 323        |

| FPGA Status LED .....                                    | 324        |

| Firmware Recovery Switch .....                           | 325        |

| 1.6. Physical Characteristics .....                      | 326        |

| 2. Electrical Specification .....                        | 327        |

| 2.1. Camera Interfaces .....                             | 328        |

| CoaXPress CXP-6 Host Interface .....                     | 329        |

| CoaXPress CXP-12 Host Interface .....                    | 331        |

| 2.2. PCI Express Interfaces .....                        | 333        |

| 4-lane Rev 3.0 PCIe end-point .....                      | 334        |

| 8-lane Rev 3.0 PCIe end-point .....                      | 335        |

| 2.3. Power .....                                         | 336        |

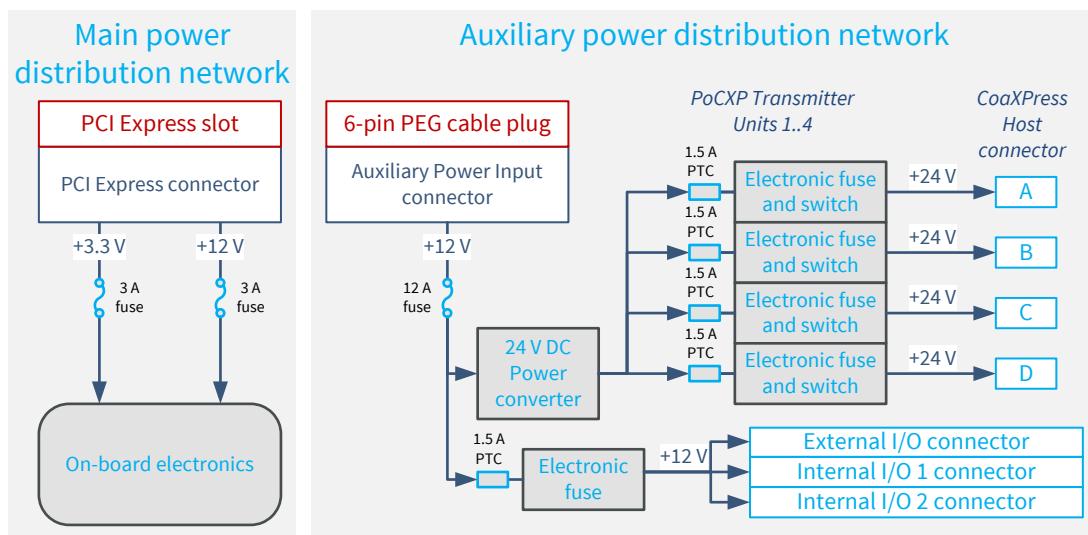

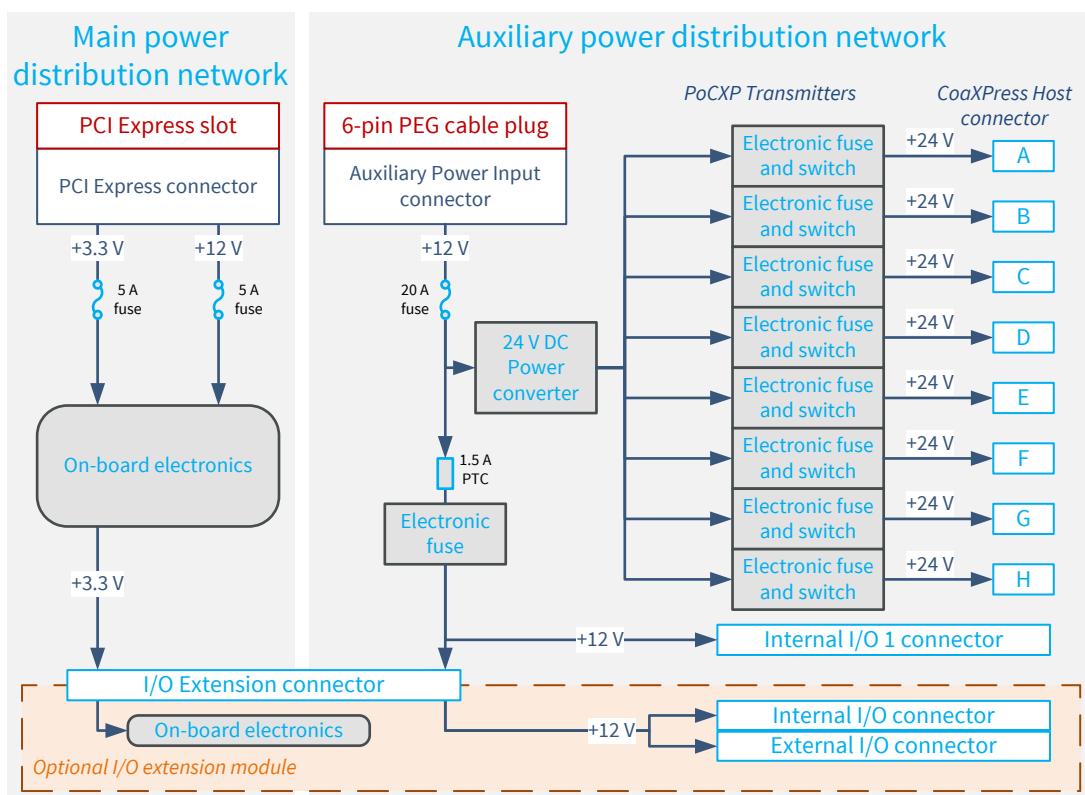

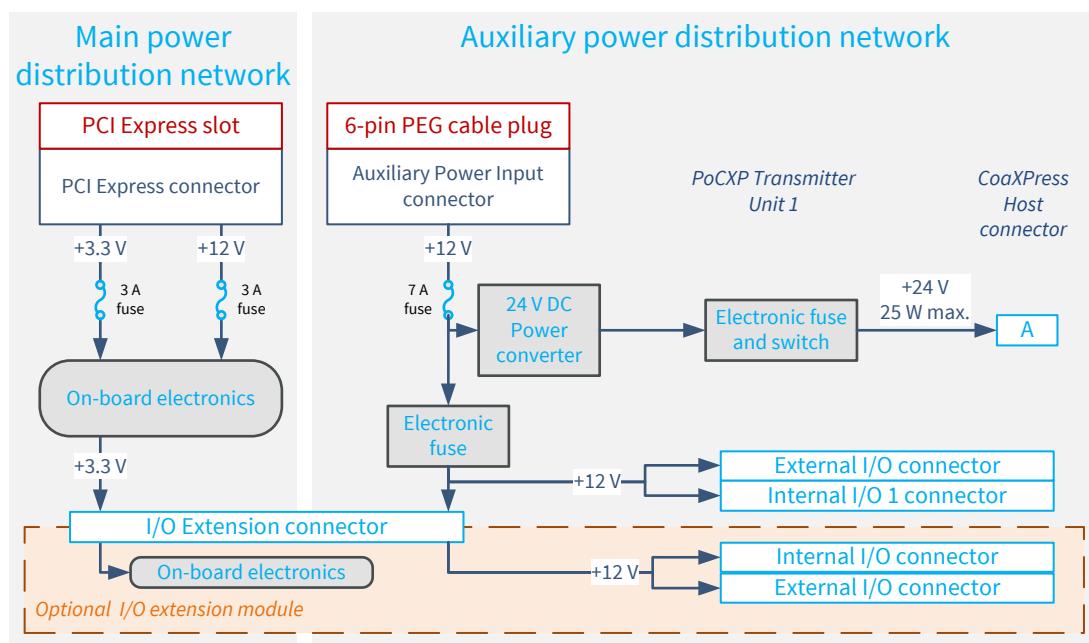

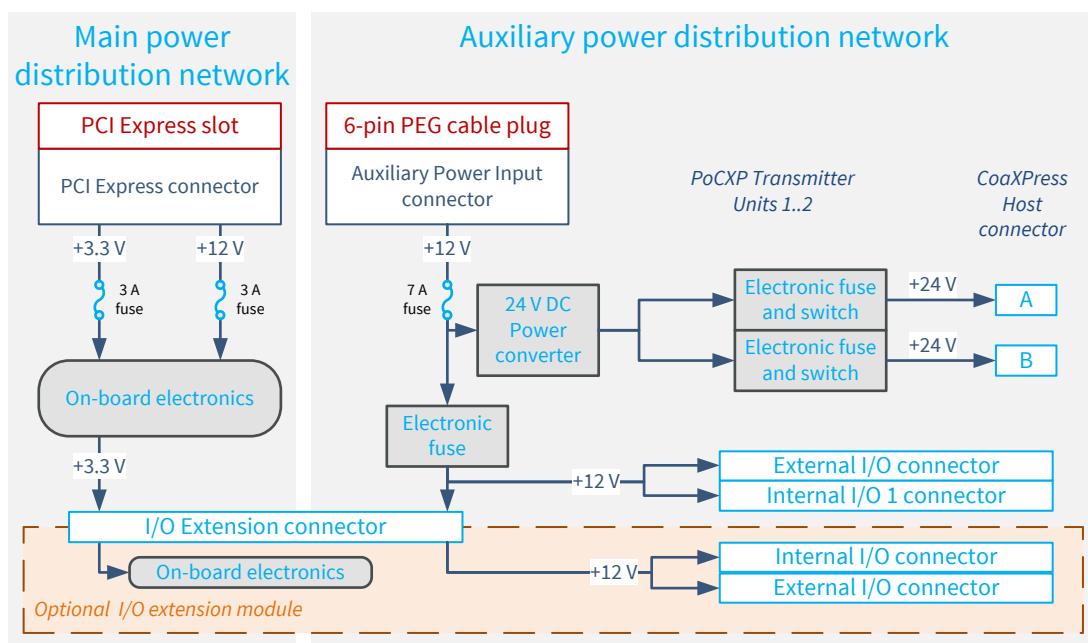

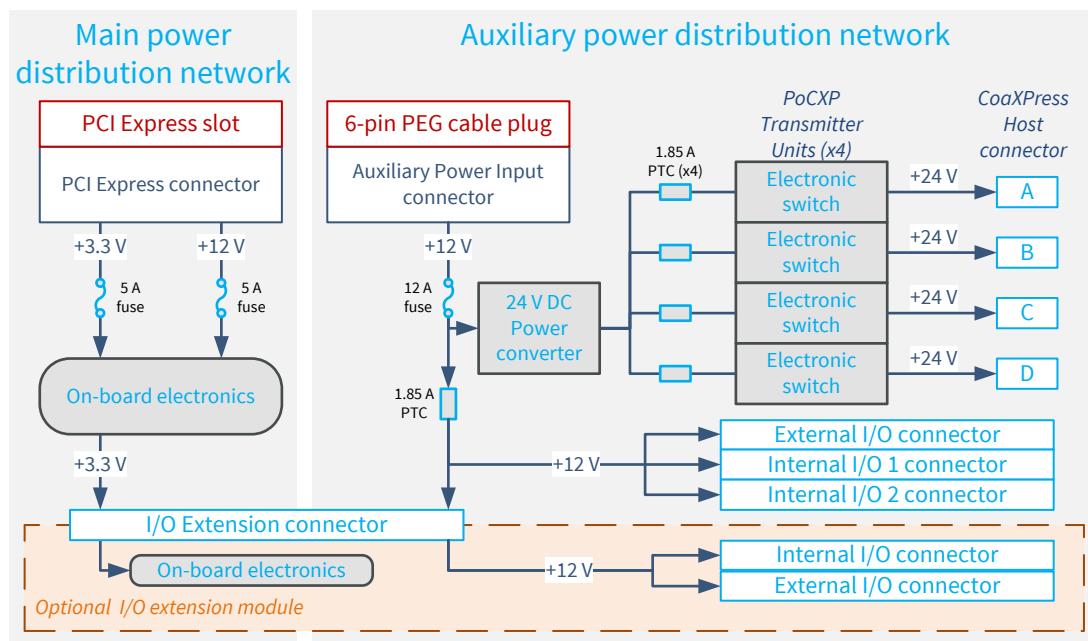

| Power Distribution Schemes .....                         | 337        |

| PC1633-T Coaxlink Quad G3 .....                          | 338        |

| PC3602-T Coaxlink Octo .....                             | 339        |

| PC3621-LH-T Coaxlink Mono CXP-12-LH .....                | 341        |

| PC3622-T Coaxlink Duo CXP-12 .....                       | 342        |

| PC3623-T Coaxlink Quad CXP-12 Value .....                | 343        |

| Main Power Input Requirements .....                      | 344        |

| Auxiliary Power Input .....                              | 345        |

| I/O Power Output .....                                   | 347        |

| PoCXP Power Output Specifications .....                  | 349        |

| 2.4. I/O Interfaces .....                                | 351        |

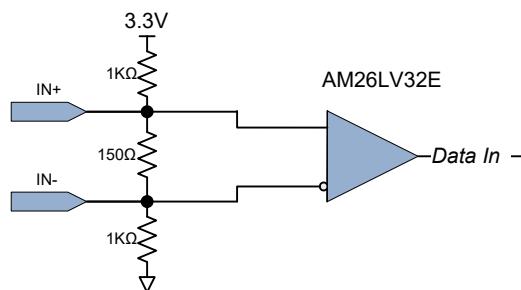

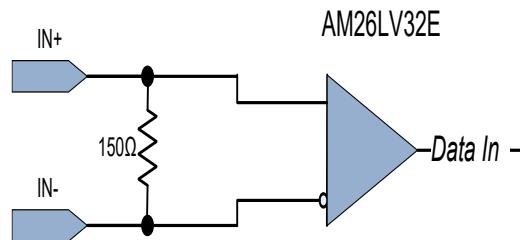

| Differential Input (Version 1) .....                     | 352        |

| Differential Input (Version 2) .....                     | 354        |

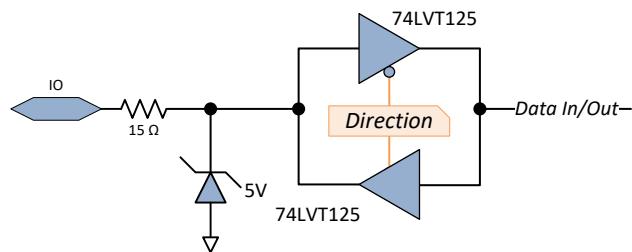

| TTL Input/Output (Version 1) .....                       | 356        |

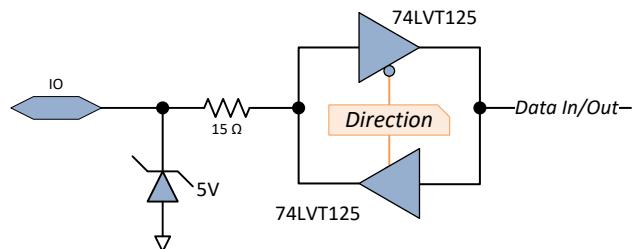

| TTL Input/Output (Version 2) .....                       | 359        |

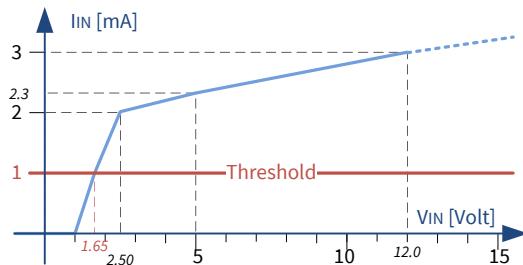

| Isolated Input (Version 1) .....                         | 362        |

|                                             |            |

|---------------------------------------------|------------|

| Isolated Input (Version 2) .....            | 365        |

| Isolated Input (Version 4) .....            | 368        |

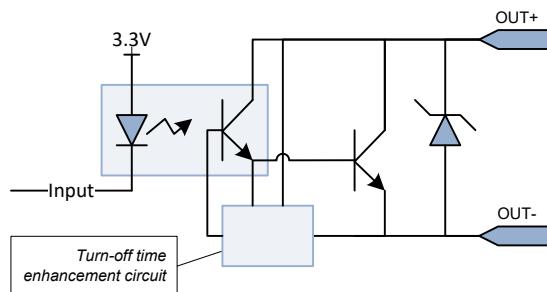

| Isolated Output .....                       | 371        |

| <b>3. Environmental Specification .....</b> | <b>374</b> |

| 3.1. Storage Conditions .....               | 375        |

| 3.2. Operating Conditions .....             | 376        |

| 3.3. Temperature Monitor .....              | 377        |

| 3.4. Thermal Design Data .....              | 380        |

| 3.5. Compliance Statements .....            | 381        |

| <b>PART IV : GENAPI FEATURES .....</b>      | <b>384</b> |

*PART I*

*GETTING STARTED*

# 1. Hardware Setup

|                                                    |    |

|----------------------------------------------------|----|

| 1.1. Precautions for Use of Board Products .....   | 9  |

| 1.2. PCI Express Card Slot Requirements .....      | 10 |

| 1.3. PCI Express Card Installation Procedure ..... | 11 |

| 1.4. Low-Profile Bracket Installation .....        | 11 |

## 1.1. Precautions for Use of Board Products

*Electrostatic Sensitive Device* Boards may be damaged by electrostatic discharges. Follow the procedure hereby described and apply any general procedure aimed at reducing the risk associated with electrostatic discharge. Damage caused by improper handling is not covered by the manufacturer's warranty.

*Electromagnetic Compatibility* AVT boards are compliant with electromagnetic compatibility regulatory requirements. To ensure this compliance, the card bracket must be secured with the relevant screw in accordance with the procedure described herein.

*Risk of Electrical Shock* Do not operate the computer with any enclosure cover removed. During the hardware installation, ensure the AC power cord is unplugged before touching any internal part of the computer.

*Risk of Burn* Do not touch an operating board. Allow board to cool before handling.

*Heating Device* It is normal for a board to dissipate some heat during operation. All enclosure covers, including blank brackets, must be fitted correctly to ensure that the fan cools the computer adequately.

*Hot Plugging Forbidden* Uncontrolled plugging and unplugging of equipment may damage a board. Always switch off the computer and any relevant system device when connecting or disconnecting a cable at the frame grabber or auxiliary board bracket. Failure to do so may damage the card and will void the warranty.

*Poor Grounding Protection* The computer and the camera can be located in distant areas with individual ground connections. Poor ground interconnection, ground loop or ground fault may induce unwanted voltage between equipment, causing excessive current in the interconnecting cables. This faulty situation can damage the frame grabber or the camera electrical interface. The user must follow proper equipment grounding practices at all ends of the interconnecting cables. In addition, the use of cable assemblies with overall shield solidly connected to the conductive shell of all connectors is recommended. Besides the beneficial effect of cable shielding on electromagnetic compatibility, the shield connection can increase the protection level against grounding problems by temporarily absorbing unwanted fault current.

## 1.2. PCI Express Card Slot Requirements

### Data transfer performance

- Products belonging to the **PCI\_3x4** group must be plugged into a x4, x8 or x16 PCI Express Gen 3 card connector providing at least four active lanes.

- Products belonging to the **PCI\_3x8** group must be plugged into a x8 or x16 PCI Express Gen 3 card connector providing at least eight active lanes.

### Powering capability

- Products belonging to the **25W** group must be plugged into a 25 W PCI Express slot

### Cooling

To guarantee reliable operation across the entire operating temperature range and longer lifetime, ensure an adequate cooling of the card:

- The cooling is improved by a higher air flow circulating around the board. This air flow is increased, for example, by using computer case fans.

- Avoid placing a card next to other heat dissipating boards.

## 1.3. PCI Express Card Installation Procedure

1. Switch off the computer and all connected peripherals (monitor, printer...).

2. Discharge any static electricity that could be accumulated by your body. You can achieve this by touching an unpainted metal part of the enclosure of your computer with a bare hand. Make sure that the computer is linked to the AC power outlet with proper earth connection.

3. Disconnect all cables from your computer, including AC power.

4. Open the computer enclosure, according to the manufacturer instructions, to gain access to the PCI Express slots. Locate an available and adequate PCI Express slot.

5. Remove the blank bracket associated with this location. To achieve this, remove the securing screw and keep it aside for later use in the procedure. Keep the blank bracket in a known place for possible re-use.

6. Unwrap the card packing, take the board and carefully hold it. Avoid any contact of the board with unnecessary items, including your clothes.

7. Gently insert the card into the selected PCIe slot, taking care to push it down fully into the slot. If you experience some resistance, remove the board and repeat the operation. You should attempt to make a perfect board-to-slot mechanical alignment for best results. Ensure that the lower part of the bracket is inserted into the corresponding enclosure fastening.

8. Secure the board with the saved screw.

9. **Optional.** When the camera(s) is (are) powered through the camera cable (PoCXP or PoCL) or when the +12 V power output is required on any System I/O connector, connect a 12 V power source to the Auxiliary Power Input connector using an 8-pin PEG cable terminated with a 2x3 plug + 2x1 plug (mandatory when total AUX power exceeds 75 W) or a 6-pin cable.

10. **Optional.** Establish the connections with the Internal GPIO connector(s) as required by the application.

11. **Optional.** When synchronized acquisition is required for cameras attached to different cards, establish the card-to-card link interconnections.

12. Close the computer enclosure according to the manufacturer instructions.

## 1.4. Low-Profile Bracket Installation

Products belonging to the **LP** group can also be installed in a low-profile computer. Therefore:

1. Remove the original standard-profile bracket by unscrewing the screw locks

2. Install the low-profile bracket and secure it on the board with the screw locks

## 2. Software Setup

|                                     |    |

|-------------------------------------|----|

| 2.1. Software Setup Procedure ..... | 12 |

| 2.2. Important Notices .....        | 12 |

| 2.3. Installing eGrabber .....      | 16 |

### 2.1. Software Setup Procedure

Prior to use the board, it is necessary to install the driver and update or install the firmware.

- The eGrabber driver is available from the *Software Downloads* page of the AVT website: <https://www.alliedvision.com/en/support/software-downloads/>

### 2.2. Important Notices

*Important notifications to be read before installing and/or using the product on your PC!*

|                              |    |

|------------------------------|----|

| Firmware Revisions .....     | 12 |

| CPU Requirements .....       | 13 |

| Image Buffer Limits .....    | 13 |

| Notice for Windows .....     | 13 |

| Notice for Linux .....       | 14 |

| Notice for NVIDIA RDMA ..... | 14 |

| Notices for macOS .....      | 15 |

### Firmware Revisions

#### WARNING

**eGrabber driver** checks the compatibility of the firmware installed on every frame grabber. For those having an incompatible firmware, the GenTL driver exposes 0 (zero) Device.

If the requirement is not satisfied for all the **eGrabber-driven frame grabbers** in your system, it is *mandatory* to apply the Firmware Upgrade procedure prior to using this version of the driver.

**NOTE**

Starting with eGrabber 25.03, the firmware revision numbers are listed, for each firmware-variant in the [Firmware Variants table](#)

## CPU Requirements

The image converter requires a CPU that has the Supplemental Streaming SIMD Extension 3 (SSSE3) instruction set.

## Image Buffer Limits

### Maximum buffer size

0xffffffff0 bytes (4 GiB - 16 B) for all operating systems

### Number of buffers

The number of buffers is only limited by available system resources.

**NOTE:** when using very large numbers of buffers, DSAnnounceBuffer calls can take longer and longer to complete (or even fail with error code GC\_ERR\_CUSTOM\_IOCTL\_BUFFER\_ANNOUNCE\_FAILED). If this happens, the user should set [DmaEngineOptimization=LowMemoryUsage](#) in the data stream module.

## Notice for Windows

*Important notifications to be read before installing and/or using the product on your Windows PC*

### Missing time-stamping certificate

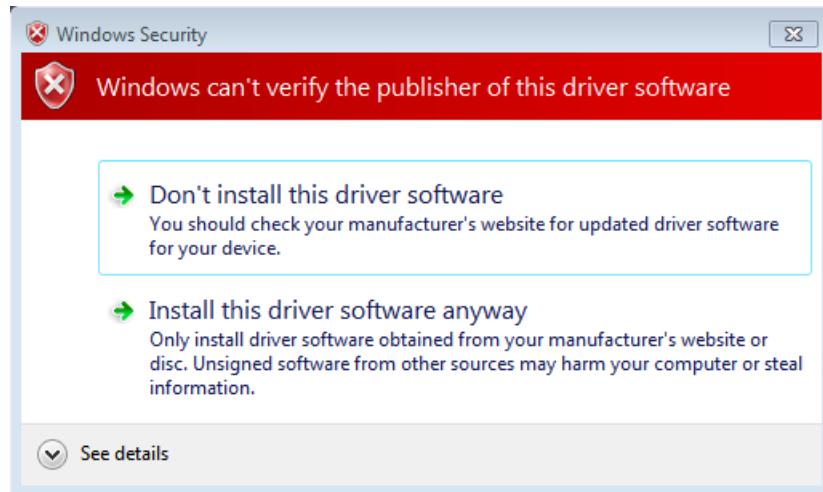

The following Windows Security warning message may occur at driver installation on Microsoft Windows:

This Windows security warning occurs when the **GlobalSign Root CA - R6** certificate is missing from the Windows certificate store.

This issue can be solved by installing this missing certificate which can be downloaded [here](#) on the GlobalSign website then installed in the Trusted Root Certification Authorities (local computer) certificate store.

## Notice for Linux

*Important notification to be read before installing and/or using the product on your Linux PC*

- **Memento** must be installed prior to **eGrabber**.

- If the **eGrabber** package is already installed, proceed as follows:

- Uninstall **eGrabber**.

- Install **Memento**.

- Re-install **eGrabber**.

- If NVIDIA RDMA is required, read "[Notice for NVIDIA RDMA](#)" on page 14

## Notice for NVIDIA RDMA

NVIDIA RDMA is only supported on Linux.

NVIDIA RDMA samples require a NVIDIA GPU that supports RDMA.

The NVIDIA RDMA samples allocate memory on the GPU and announce this memory using `NvidiaRdmaMemory`.

See the following files in the eGrabber sample programs:

- `cpp/egrabber/samples/503-grabn-cuda-rdma-process.*`

- `cpp/nvidia/egrabber-cuda` with the command line argument `cudaRDMA`

## Installation instructions:

---

- NVIDIA CUDA drivers:

- Follow the installation instructions from: [https://developer.nvidia.com/cuda-downloads?target\\_os=Linux&target\\_arch=x86\\_64&Distribution=Ubuntu&target\\_version=20.04&target\\_type=deb\\_network](https://developer.nvidia.com/cuda-downloads?target_os=Linux&target_arch=x86_64&Distribution=Ubuntu&target_version=20.04&target_type=deb_network)

- NVIDIA driver sources:

- These are needed to produce the Module.symvers file associated with the installed nvidia driver. This file will be required to install the eGrabber package

- Select the appropriate driver from <https://www.nvidia.com/download/index.aspx?lang=en-us>

- Make sure to download the version that matches the nvidia-<version> already installed in /usr/src/

- Extract the archive with -x option

- Change to directory kernel in the extracted archive

- Run make module

- The file Module.symvers should have been generated

- eGrabber package

- Extract the egrabber-linux-x86\_64 archive

- Install the package with the following command:

`sudo NVIDIA_KERNEL_PATH=<dir path containing Module.symvers> ./install.sh`

The line Enabling NVIDIA RDMA build should appear during the installation of the eGrabber package.

A successful build can be confirmed if the command `lsmod | grep coaxlink` (or `lsmod | grep grablink`) indicates that coaxlink (or grablink) module depends on nvidia.

## Notices for macOS

*Important notifications to be read before installing the driver on your Mac*

### Driver types

---

Install the **Memento** package corresponding to the **eGrabber** driver type:

| eGrabber driver package                                          | Memento package                                                 |

|------------------------------------------------------------------|-----------------------------------------------------------------|

| <code>egrabber-macos-aarch64-dext-&lt;MA.MI.RE.BU&gt;.pkg</code> | <code>memento-macos-aarch64-dext-&lt;MA.MI.RE.BU&gt;.pkg</code> |

| <code>egrabber-macos-aarch64-kext-&lt;MA.MI.RE.BU&gt;.pkg</code> | <code>memento-macos-aarch64-kext-&lt;MA.MI.RE.BU&gt;.pkg</code> |

| <code>egrabber-macos-x86_64-kext-&lt;MA.MI.RE.BU&gt;.pkg</code>  | <code>memento-macos-x86_64-kext-&lt;MA.MI.RE.BU&gt;.pkg</code>  |

#### TIP

dext drivers operate in user-mode using the default Full Security policy level. It is not necessary to change the security setting.

## Reduced Security level (only for kext drivers on Mac computers with Apple silicon)

---

Kernel extensions must be explicitly enabled before the installation of **AVT** -aarch64-kext-packages on Mac computers with Apple silicon.

See <https://support.apple.com/fr-be/guide/security/sec8e454101b/web>

To enable kernel extensions on a Mac with Apple silicon:

1. Enter macOS recovery

2. In **Utilities > Startup Security Utility > Security Policy**

- a. Select **Reduced Security**

- b. Check **Allow user management of kernel extensions from identified developers**

3. Restart the system

## Step 3. Approval of kernel extension (only for kext drivers on Mac computers with Apple silicon)

---

After installing **eGrabber** or **Memento** **AVT**-aarch64-kext packages, newly installed **AVT** kernel extensions must be approved by the administrator in the **Security and Privacy preferences** and the system needs to be restarted.

## 2.3. Installing eGrabber

|                                           |    |

|-------------------------------------------|----|

| Installing eGrabber on Windows .....      | 16 |

| Installing eGrabber on Linux .....        | 17 |

| Installing eGrabber on macOS .....        | 17 |

| Command-Line Installation Procedure ..... | 19 |

## Installing eGrabber on Windows

1. Read the "Notice for Windows" on page 13

1. Open the *Software Downloads* page of the **AVT** website:

<https://www.alliedvision.com/en/support/software-downloads/>

2. Expand the \*\*\*TBD\*\*\* section to display the file list corresponding to the latest available **eGrabber** release.

3. Select the **egrabber-win-x86\_64-25.07.1.\*.exe** setup file.

4. Launch the installer tool to install the driver files and software tools on your PC.

**NOTE:** If you have an existing **eGrabber** installation, the installer tool prompts you to uninstall it before being able to continue. Otherwise, it prompts you for the selection of the destination folder.

## Installing eGrabber on Linux

1. Read the "Notice for Linux" on page 14

1. Open the *Software Downloads* page of the AVT website:

<https://www.alliedvision.com/en/support/software-downloads/>

2. Expand the \*\*\*TBD\*\*\* section to display the file list corresponding to the latest available eGrabber release.

3. Download the setup file according to the processor architecture:

- For an installation on AArch64 (64-bit) processor architecture, select the egrabber-linux-aarch64-25.07.1.\*.tar.gz setup file.

- For an installation on x86\_64 (64-bit) processor architecture, select the egrabber-linux-x86\_64-25.07.1.\*.tar.gz setup file.

4. Extract the egrabber-linux-<ARCH>-<VERSION>.tar.gz archive, e.g., with tar -xaf egrabber-linux-<ARCH>-<VERSION>.tar.gz

5. Run the installation script: sudo ./egrabber-linux-<ARCH>-<VERSION>/install.sh

### NOTE

- If you have an existing eGrabber installation, the installer tool prompts you to uninstall it before being able to continue. Otherwise, it prompts you for the selection of the destination folder.

- After installation, sudo /opt/euresys/egrabber/shell/check-install.sh can be executed to check the eGrabber installation and troubleshoot issues.

## Installing eGrabber on macOS

1. Read the "Notices for macOS" on page 15.

1. Open the *Software Downloads* page of the AVT website:

<https://www.alliedvision.com/en/support/software-downloads/>

2. Expand the \*\*\*TBD\*\*\* section to display the file list corresponding to the latest available eGrabber release.

3. Execute the installation procedure according to the processor architecture and the driver type:

## Installing dext packages on Mac computers with Apple silicon

1. Download egrabber-macos-aarch64-dext-25.07.1.\*.pkg

2. After package files have been downloaded with *Safari*, the usual *double-click* to launch the installer will not let you install the package. You shall use instead *control+click* and select *Open* to launch the installer. A window will pop up, click then on *Open* to proceed.

The extension installer applications will be launched automatically and will be waiting for the administrator to approve the newly installed **AVT** extensions in the **Security and Privacy preferences**.

3. Launch the installer tool to install the driver files and software tools on your PC.

## Installing kext drivers packages on Mac computers with Apple silicon

### Step 1. Enable kernel extensions

Kernel extensions must be explicitly enabled before the installation of **AVT** -aarch64-kext-packages on Mac computers with Apple silicon.

See <https://support.apple.com/fr-be/guide/security/sec8e454101b/web>

To enable kernel extensions on a Mac with Apple silicon:

1. Enter macOS recovery

2. In **Utilities > Startup Security Utility > Security Policy**

- a. Select **Reduced Security**

- b. Check **Allow user management of kernel extensions from identified developers**

3. Restart the system

### Step 2 Launch the installer

1. Download egrabber-macos-aarch64-kext-25.07.1.\*.pkg

2. After package files have been downloaded with *Safari*, the usual *double-click* to launch the installer will not let you install the package. You shall use instead *control+click* and select *Open* to launch the installer. A window will pop up, click then on *Open* to proceed.

### Step 3. Approve kernel extension

After installing **eGrabber** or **Memento** **AVT** -aarch64-kext packages, newly installed **AVT** kernel extensions must be approved by the administrator in the **Security and Privacy preferences** and the system needs to be restarted.

## Installing kext drivers packages on Mac computers with an Intel processor

1. Download egrabber-macos-x86\_64-kext-25.07.1.\*.pkg

2. After package files have been downloaded with *Safari*, the usual *double-click* to launch the installer will not let you install the package. You shall use instead *control+click* and select *Open* to launch the installer. A window will pop up, click then on *Open* to proceed.

# Command-Line Installation Procedure

You may want to integrate the boards drivers and eGrabber tools installation into your own application distribution.

eGrabber setup program can be called in command-line mode with your installation options. In this mode, the eGrabber installation program does not prompt for user action and does not display any dialog box.

## Installation

To perform a command-line installation, call the setup program with the /s flag. The installation is launched in the silent mode, that is no window nor dialog box will appear.

There are a couple of optional flags:

- Use the /a flag to force the installation of all components, including optional ones which are not selected by default.

- Use the /fflag to force the removal of an already installed version before executing the setup file, even if the already installed version is newer.

## Installation removal

To automatically remove installed tools, call the setup program with the /u flag.

Use the /s flag to launch the removal program in the silent mode. In this mode, no window nor dialog box will appear.

## Reboot during Installation

A reboot may be required after driver installation but will not take place automatically. The reboot must be performed by your application. In this case, the [HKEY\_LOCAL\_MACHINE\SOFTWARE\Euresys\Common] "RebootNeeded" registry entry should be checked. If it exists and is set to 1, then it should be replaced by 0, and the system must be rebooted.

## Error Reporting

After the command line installation, the following registry key is updated and holds the installation status: [HKEY\_LOCAL\_MACHINE\SOFTWARE\Euresys\Common\LastInstallError].

- The ErrorCode DWORD identifies the error:

- 0 - There is no error.

- Any other value - Please contact technical support.

- The Cause string gives a wording of the error.

- The Source string identifies the installer that caused the error.

- The ErrorTime string gives the time and date of the error.

## 3. Managing Firmware

|                                       |    |

|---------------------------------------|----|

| 3.1. What's Firmware?                 | 21 |

| 3.2. Firmware Manager Tools           | 22 |

| 3.3. Updating and Installing Firmware | 24 |

| 3.4. Firmware Recovery Switch         | 25 |

## 3.1. What's Firmware?

### Firmware

In this context, "firmware" designates the content of the FPGA (Field Programmable Gate Array) device of a card.

It defines the functionality of the card including the PCI Express end-point.

### Firmware EEPROM

The FPGA used on **eGrabber-driven frame grabbers** is RAM-based; it needs to be loaded every power up.

Considering that a PCI Express end point must be ready within 150 milliseconds of the power-up time, the FPGA content, must be loaded quickly after having applied power to the card.

Therefore, the firmware is stored into a non-volatile flash EEPROM allowing a fast start-up of the FPGA.

#### TIP

The **eGrabber** driver will never modify the content of the FPGA during operation.

### Firmware modifications

Any modification of the FPGA content requires a two-step operation:

1. The new firmware is written into the Flash EEPROM of the card using a firmware management tool.

2. The new firmware is activated by cycling the system power.

## 3.2. Firmware Manager Tools

eGrabber is delivered with two firmware management tools:

- "Firmware Manager - GUI mode" on page 22 : A graphical user interface tool in **eGrabber Studio**,

- "Firmware Manager - Command line mode" on page 22 : A command-line tool named **Firmware Manager Console**.

### Firmware Manager - GUI mode

To open the **Firmware Manager** in GUI mode, select one of the following methods:

- From the Windows Start Menu: click on Firmware Manager shortcut in the **Euresys eGrabber** folder

- From the **Welcome Screen** of **eGrabber Studio**, click on the **Firmware Manager** button.

**See also:** "Firmware Manager (GUI mode)" section in the **eGrabber Studio User Guide** for a detailed description.

### Firmware Manager - Command line mode

#### Access

The command-line tool is named coaxlink-firmware.exe. It is located in the firmware sub-folder folder of the eGrabber installation folder.

On Windows, to open the **Firmware Manager** in command-line mode, select one of the following methods:

- From the Windows Start Menu: click on Firmware Manager console shortcut in the **Euresys eGrabber** folder

- Open a command prompt and open in the C:\Program Files\Euresys\egrabber\firmware folder

On Linux, to open the **Firmware Manager** in command-line mode:

- Open a command shell in the /opt/euresys/egrabber/firmware folder

On macOS, to open the **Firmware Manager** in command-line mode:

- Open a command shell in the /usr/local/opt/euresys/egrabber/firmware folder.

#### Main commands

- Executing coaxlink-firmware --help displays a help message describing all the command options.

- Executing coaxlink-firmware gui starts the **Firmware Manager (Deprecated)** graphical user interface.

- Executing coaxlink-firmware list lists the properties of the firmware installed on each card present in the system.

- Executing coaxlink-firmware update updates the firmware.

- Executing coaxlink-firmware install installs a new firmware variant.

Unless specified with a --firmware=FILE option, the tool uses the embedded library.

### 3.3. Updating and Installing Firmware

#### WARNING

Prior to executing this procedure, read the "Important Notices" section of the release notes!

The **eGrabber** driver comes with all the firmware variants for all the **eGrabber-driven frame grabbers**.

1. Determine the firmware variant that fulfills the functional requirements of your application: e.g. '1-camera', '1-camera, line-scan', '2-camera'. Therefore, check the *Firmware Variants per Product* section of the release notes for the firmware variants that are applicable to your card.

2. Launch a **Firmware Manager tool** to perform a firmware *update* or to *install* a specific firmware variant on your card(s) using the **Firmware Manager** tool in *GUI mode* with **eGrabber Studio** or the **Firmware Manager Console** in *command-line mode*:

- a. In **eGrabber Studio**, open the **Firmware Manager** pane:

- Select the card to update

- Select the firmware variant to install

- Proceed with the installation

- b. In command-line mode, to *update* a variant:

`coaxlink-firmware update`

- c. In command-line mode, to *install* another firmware variant:

`coaxlink-firmware install '[variant-name]'`

3. Wait until completion of the firmware update

#### WARNING

Avoid turning off your PC during the firmware update procedure!

4. Repeat the procedure on all your **eGrabber-driven frame grabbers**.

5. **Power off completely** your PC and restart it to activate the newly loaded firmware.

## 3.4. Firmware Recovery Switch

### Switch types and location

The *firmware recovery switch* is implemented with one of the following components:

- 3-pin header and a jumper

- 2-way DIP switch

**See also:** "Product Layouts" on page 294 in the Handbook to locate the firmware recovery switch. .

### Switch positions

The *firmware recovery switch* has two positions:

#### Normal position (factory default)

At the next power ON, the latest firmware successfully written into the Flash EEPROM is used to program the FPGA. After FPGA startup completion, the card exhibits the *standard PCI ID* and the driver allows normal operation.

#### Recovery position

At the next power ON, the last but one firmware successfully written into the Flash EEPROM is used to program the FPGA. After FPGA startup completion, the card exhibits the *recovery PCI ID* and the driver inhibits image acquisition.

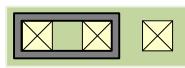

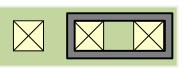

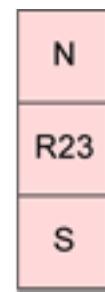

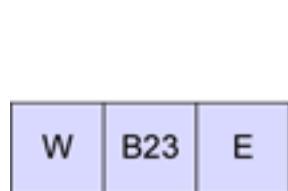

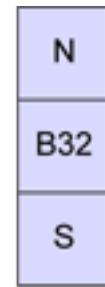

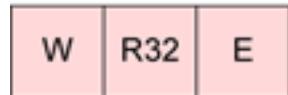

| Switch type               | Normal position                                                                     | Recovery position                                                                     |

|---------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 3-pin header and a jumper |  |  |

| 2-way DIP switch          |  |  |

## 4. Firmware Variants

This topic shows, for each officially supported product (group), the list of officially available<sup>1</sup> firmware variants provided with eGrabber 25.07.

- The **Firmware variant** column shows the name of the firmware variant.

- The **HCMAP** column shows the [Host Connection Map](#)<sup>2</sup>.

- The **Features** column shows the main features of the firmware variant.

- The **Description** column shows a one-phrase description of the connection scheme.

- The **Rev.** column shows the revision number of the firmware delivered with this release.

### PC1633-T Coaxlink Quad G3

| Firmware Variant        | HCMAP  | Features       | Description                                                          | Rev. |

|-------------------------|--------|----------------|----------------------------------------------------------------------|------|

| 1-camera                | 1D4    | FFC LUT CFA-12 | One 1- or 2- or 4-connection area-scan camera                        | 481  |

| 1-camera, 4-data-stream | 1D4S4  |                | One 1- or 2- or 4-connection area-scan camera, up to 4 data streams  | 481  |

| 1-camera, line-scan     | 1D4    | FFC LUT FLIPX  | One 1- or 2- or 4-connection line-scan camera                        | 481  |

| 2-camera                | 2D22   | LUT CFA-35-D0  | One or two 1- or 2-connection area-scan cameras                      | 481  |

| 2-camera, bayer         | 2D22   | CFA-35         | One or two 1- or 2-connection area-scan cameras                      | 481  |

| 2-camera, line-scan     | 2D22   | LUT            | One or two 1- or 2-connection line-scan cameras                      | 481  |

| 3-camera                | 3D211  | LUT            | One 1- or 2-connection and one or two 1-connection area-scan cameras | 481  |

| 4-camera                | 4D1111 | LUT            | One or two or three or four 1-connection area-scan cameras           | 481  |

| 4-camera, line-scan     | 4D1111 | LUT            | One or two or three or four 1-connection line-scan cameras           | 481  |

<sup>1</sup> Excluding custom firmware variants

<sup>2</sup> Specific assignment of the Device connections to the Host connectors

## PC3602-T Coaxlink Octo

| Firmware Variant    | HCMAP     | Features               | Description                                                                                 | Rev. |

|---------------------|-----------|------------------------|---------------------------------------------------------------------------------------------|------|

| 1-camera            | 1D8       | LUT CFA-123            | One 1- or 2- or 4- or 8-connection area-scan camera                                         | 481  |

| 1-camera, line-scan | 1D8       | LUT MI                 | One 1- or 2- or 4- or 8-connection line-scan camera                                         | 481  |

| 2-camera            | 2D44      | FFC LUT CFA-125        | One or two 1- or 2- or 4-connection area-scan cameras                                       | 481  |

| 2-camera, line-scan | 2D44      | LUT FLIPX MI<br>PLANAR | One or two 1- or 2- or 4-connection line-scan cameras                                       | 481  |

| 3-camera            | 3D422     | LUT                    | One 1- or 2- or 4-connection and one or two 1- or 2-connection area-scan cameras            | 481  |

| 4-camera            | 4D2222    | LUT                    | One or two or three or four 1- or 2-connection area-scan cameras                            | 481  |

| 4-camera, line-scan | 4D2222    | LUT MI                 | One or two or three or four 1- or 2-connection line-scan cameras                            | 481  |

| 5-camera            | 5D41111   | LUT                    | One 1- or 2- or 4-connection and one or two or three or four 1-connection area-scan cameras | 481  |

| 5-camera, 5D22211   | 5D22211   | LUT                    | One or two or three 1- or 2-connection and one or two 1-connection area-scan cameras        | 481  |

| 8-camera            | 8D1111111 | LUT                    | Up to eight 1-connection area-scan cameras                                                  | 481  |

| 8-camera, line-scan | 8D1111111 | LUT MI                 | Up to eight 1-connection line-scan cameras                                                  | 481  |

## PC3621-LH-T Coaxlink Mono CXP-12-LH

| Firmware Variant    | HCMAP | Features | Description                       | Rev. |

|---------------------|-------|----------|-----------------------------------|------|

| 1-camera            | 1D1   | LUT      | One 1-connection area-scan camera | 481  |

| 1-camera, line-scan | 1D1   | LUT      | One 1-connection line-scan camera | 481  |

## PC3622-T Coaxlink Duo CXP-12

| Firmware Variant    | HCMAP | Features  | Description                               | Rev. |

|---------------------|-------|-----------|-------------------------------------------|------|

| 1-camera            | 1D2   | LUT CFA-3 | One 1- or 2-connection area-scan camera   | 481  |

| 1-camera, line-scan | 1D2   | LUT       | One 1- or 2-connection line-scan camera   | 481  |

| 2-camera            | 2D11  | LUT       | One or two 1-connection area-scan cameras | 481  |

| 2-camera, line-scan | 2D11  | LUT       | One or two 1-connection line-scan cameras | 481  |

## PC3623-T Coaxlink Quad CXP-12 Value

| Firmware Variant    | HCMAP  | Features           | Description                                                          | Rev. |

|---------------------|--------|--------------------|----------------------------------------------------------------------|------|

| 1-camera            | 1D4    | FFC LUT CFA-12 BIN | One 1- or 2- or 4-connection area-scan camera                        | 481  |

| 1-camera, line-scan | 1D4    | FFC LUT BIN MI LT  | One 1- or 2- or 4-connection line-scan camera                        | 481  |

| 2-camera            | 2D22   | LUT                | One or two 1- or 2-connection area-scan cameras                      | 481  |

| 2-camera, line-scan | 2D22   | LUT MI LT          | One or two 1- or 2-connection line-scan cameras                      | 481  |

| 3-camera            | 3D211  | LUT                | One 1- or 2-connection and one or two 1-connection area-scan cameras | 481  |

| 4-camera            | 4D1111 | LUT                | One or two or three or four 1-connection area-scan cameras           | 481  |

| 4-camera, line-scan | 4D1111 | LUT MI             | One or two or three or four 1-connection line-scan cameras           | 481  |

## Features abbreviations

---

- *BIN*: Pixel binning

- *CFA-12*: Bayer CFA decoding - Methods 1 and 2

- *CFA-123*: Bayer CFA decoding - Methods 1, 2, and 3

- *CFA-125*: Bayer CFA decoding - Methods 1, 2, and 5

- *CFA-2-S0*: Bayer CFA decoding - Method 2 on Stream0

- *CFA-3*: Bayer CFA decoding - Method 3

- *CFA-35*: Bayer CFA decoding - Methods 3 and Method 5

- *CFA-35-D0*: Bayer CFA decoding - Methods 3 and 5 on Device0

- *FLIPX*: Horizontal image flipping

- *FFC*: Flat-field correction

- *JPEG-S1*: JPEG encoding on Stream1

- *LLE*: Laser line extraction

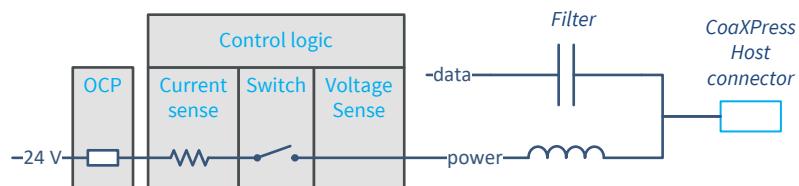

- *LT*: Mapping of events from the I/O Toolbox to CoaXPress trigger messages LinkTrigger0 and LinkTrigger1

- *LUT*: Lookup table processing

- *MI*: Metadata insertion

- *PLANAR*: RGB to PLANAR\_RGB or BGR to PLANAR\_BGR conversions

*PART II*

*FUNCTIONAL GUIDE*

# 1. Architecture of eGrabber-driven frame grabbers

|                                  |           |

|----------------------------------|-----------|

| <b>1.1. Main Elements</b> .....  | <b>31</b> |

| <b>1.2. Block Diagrams</b> ..... | <b>33</b> |

## 1.1. Main Elements

*Quick overview of the main functional elements of eGrabber-driven frame grabbers*

### GenTL hierarchy

---

Each functional element of a frame grabber is configured and controlled by GenApi features belonging to a GenTL module.

At the top of the hierarchy, there is one *GenTL System Module* per Host PC. It binds all the *GenTL Interface Modules* of a Host PC.

There is one *GenTL Interface Module* for each frame grabber. It binds all the *GenTL Device Modules* of a frame grabber.

There is one *GenTL Device Module* for each camera (or imaging device) attached to a frame grabber. The elements belonging to the imaging device (camera) itself are referred as *Remote Device*. By opposition, the elements belonging to the frame grabber are also referred as *Local Device*.

**NOTE:** The maximum number of cameras that can be attached to a frame grabber is determined by the installed firmware variant.

There is one *GenTL Data Stream Module* for each data stream delivered by a camera attached to a frame grabber. It gathers the elements involved into the image build-up and transport from the imaging device to a pool of GenTL buffers.

**NOTE:** The maximum number of data-stream for a camera attached to a frame grabber is determined by the installed firmware variant.

There is one *GenTL Buffer Module* for each image buffer.

### Main elements of the Interface Module

---

#### General purpose I/O lines

The "General Purpose I/O" on page 220 block gathers all the I/O ports of the card.

#### I/O Toolbox

The "I/O Toolbox" on page 238 block gathers a collection of tools used to build event streams from trigger and encoder devices attached to the I/O port inputs.

**NOTE:** These elements are common to- (or can be shared by-) all the GenTL Device Modules managed by the frame grabber.

## Main elements of the Device Module

---

### Camera and illumination controller

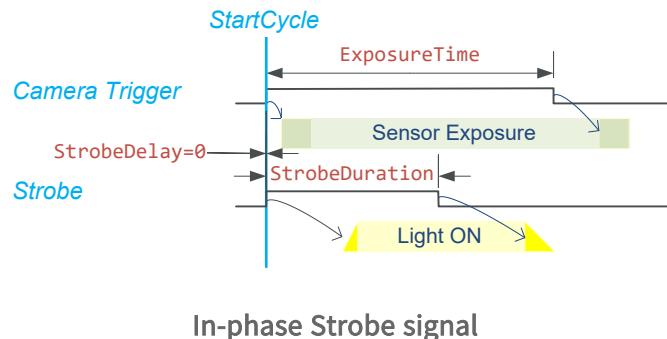

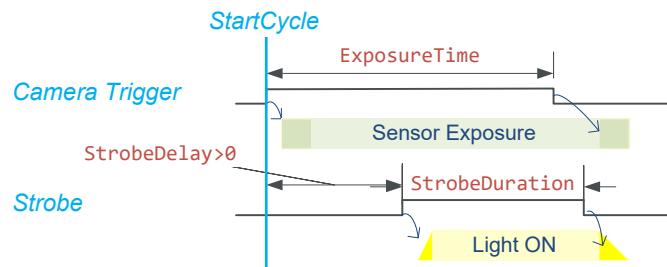

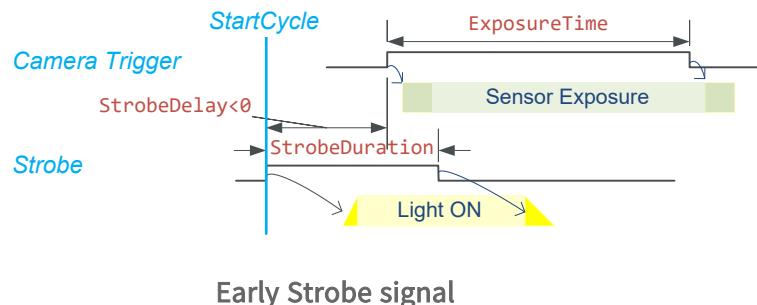

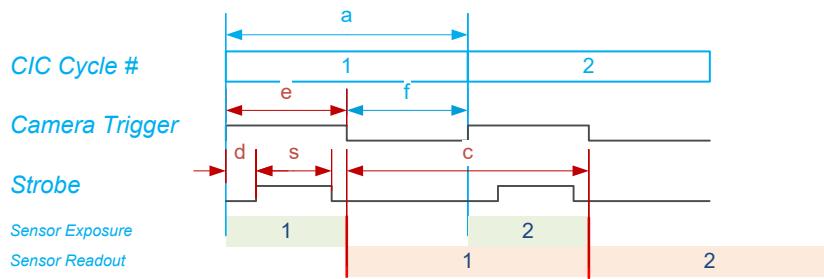

The "Camera and Illumination Control" on page 187 block is used to control the camera cycle and the illumination strobe. It can be configured to receive real-time (Camera) Cycle trigger events from any I/O Toolbox output stream. It produces two real-time signals: the **Camera Trigger** signal, sent to the camera trigger input, and the **Strobe** signal, sent to the illumination device associated with the camera.

**NOTE:** This element is common to- (or can be shared by-) all the GenTL Data Stream Modules related to that imaging device.

## Main elements of the Data Stream Module

---

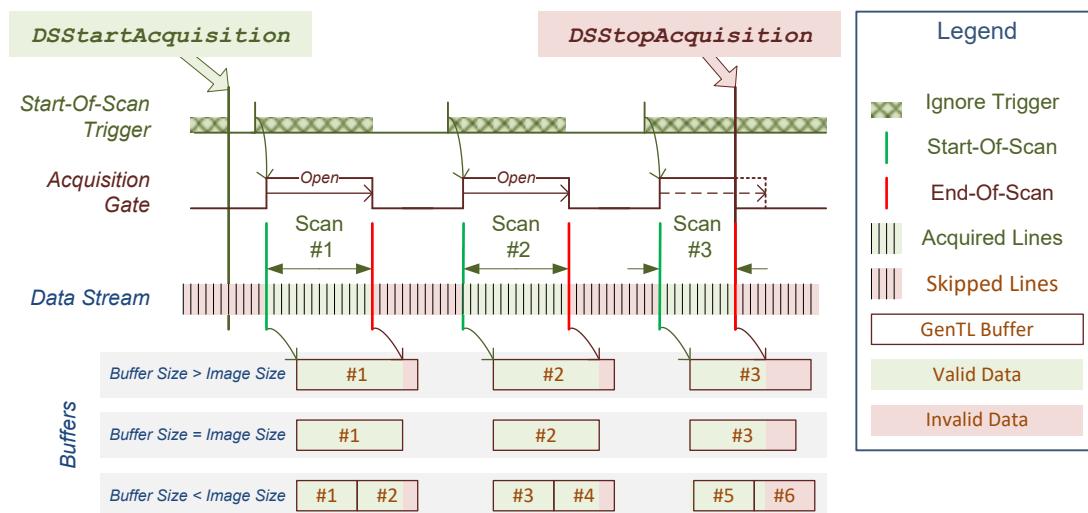

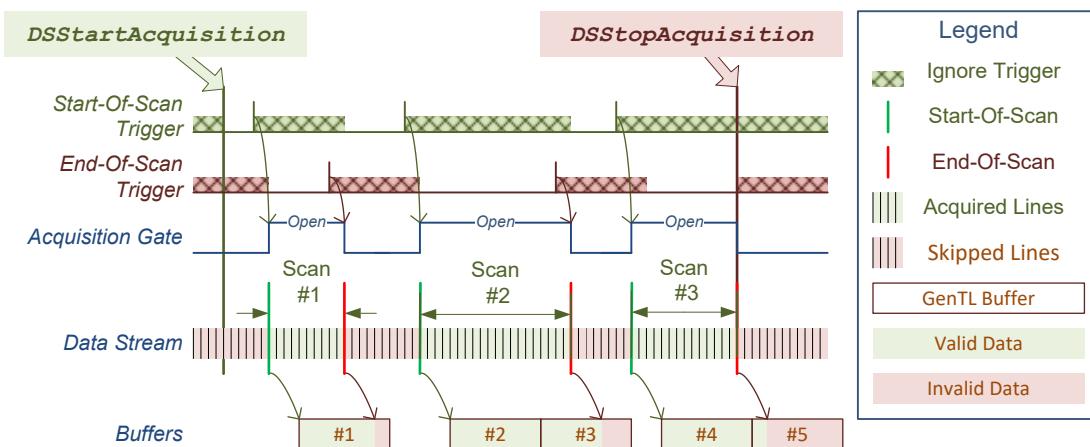

### Image acquisition controller

This block controls the acquisition gate. It can be configured to receive real-time start-of-scan and end-of-scan trigger events from any I/O Toolbox output stream.

### Acquisition gate

The "Acquisition Gate" on page 87 controls the data extraction and filters out the image data that doesn't need to be acquired.

### On-board memory

The Image data partitions of the "On-board Memory" on page 78 temporarily stores the raw image data together with related metadata such as image size, pixel type, time-stamp...

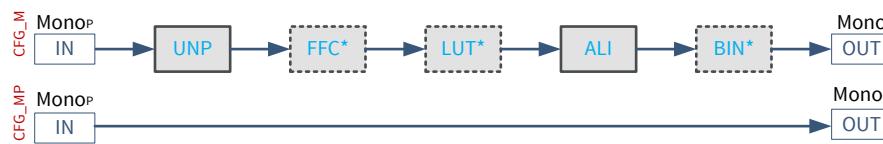

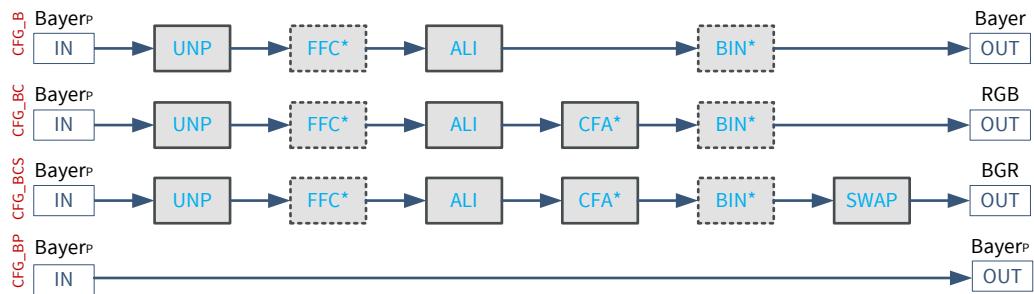

### Pixel Processing

The "Pixel Processing" on page 107 block performs on-the-fly pixel processing and data formatting.

### Image Data Transfer

The "Image Data Transfer" on page 166 block transfers the image data to the destination buffer.

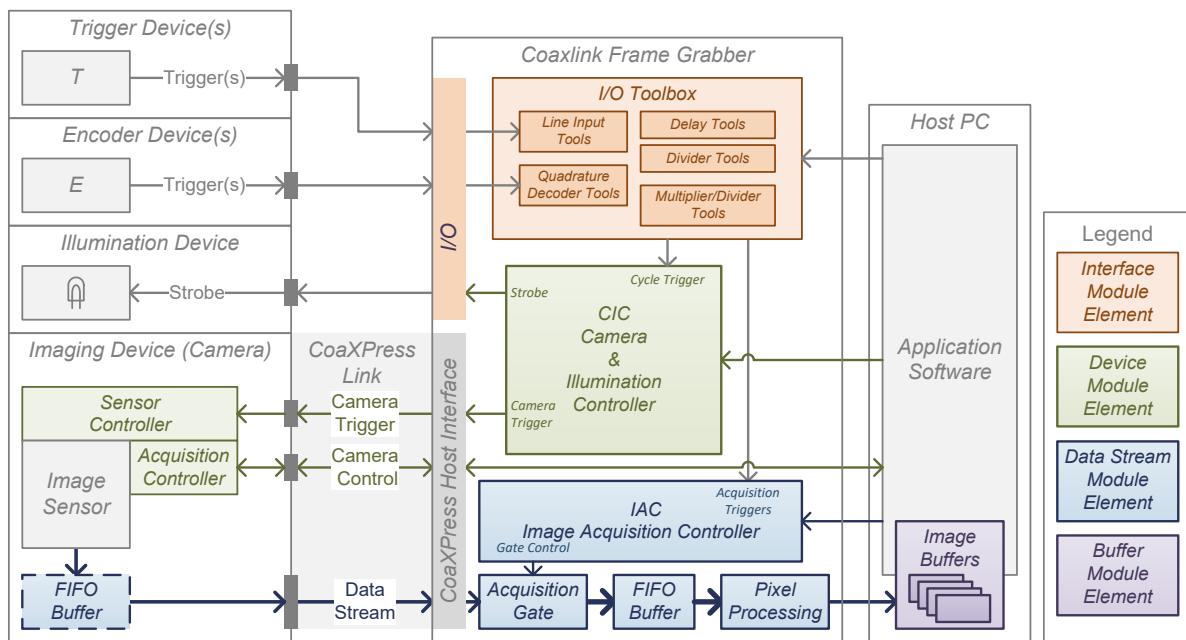

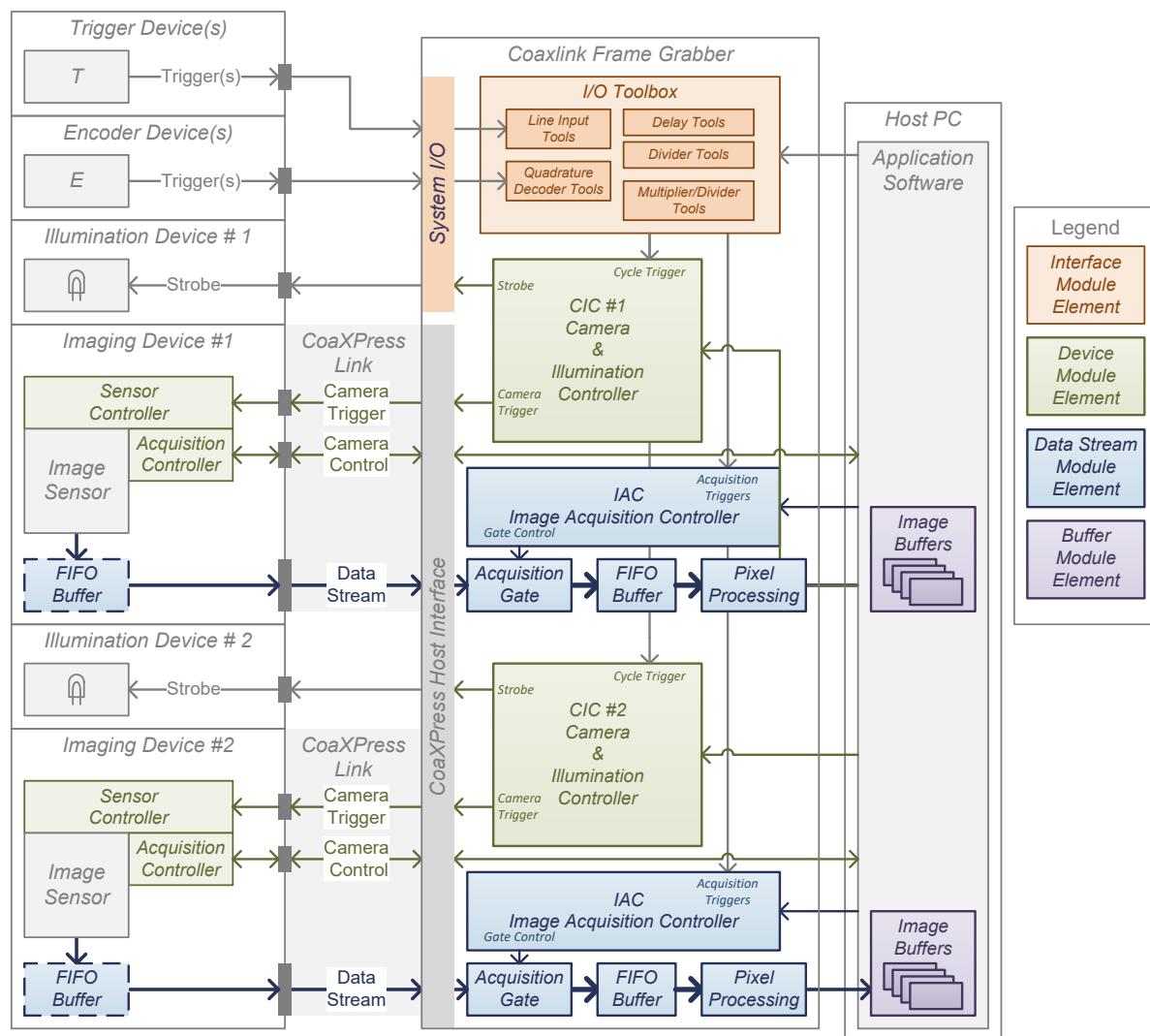

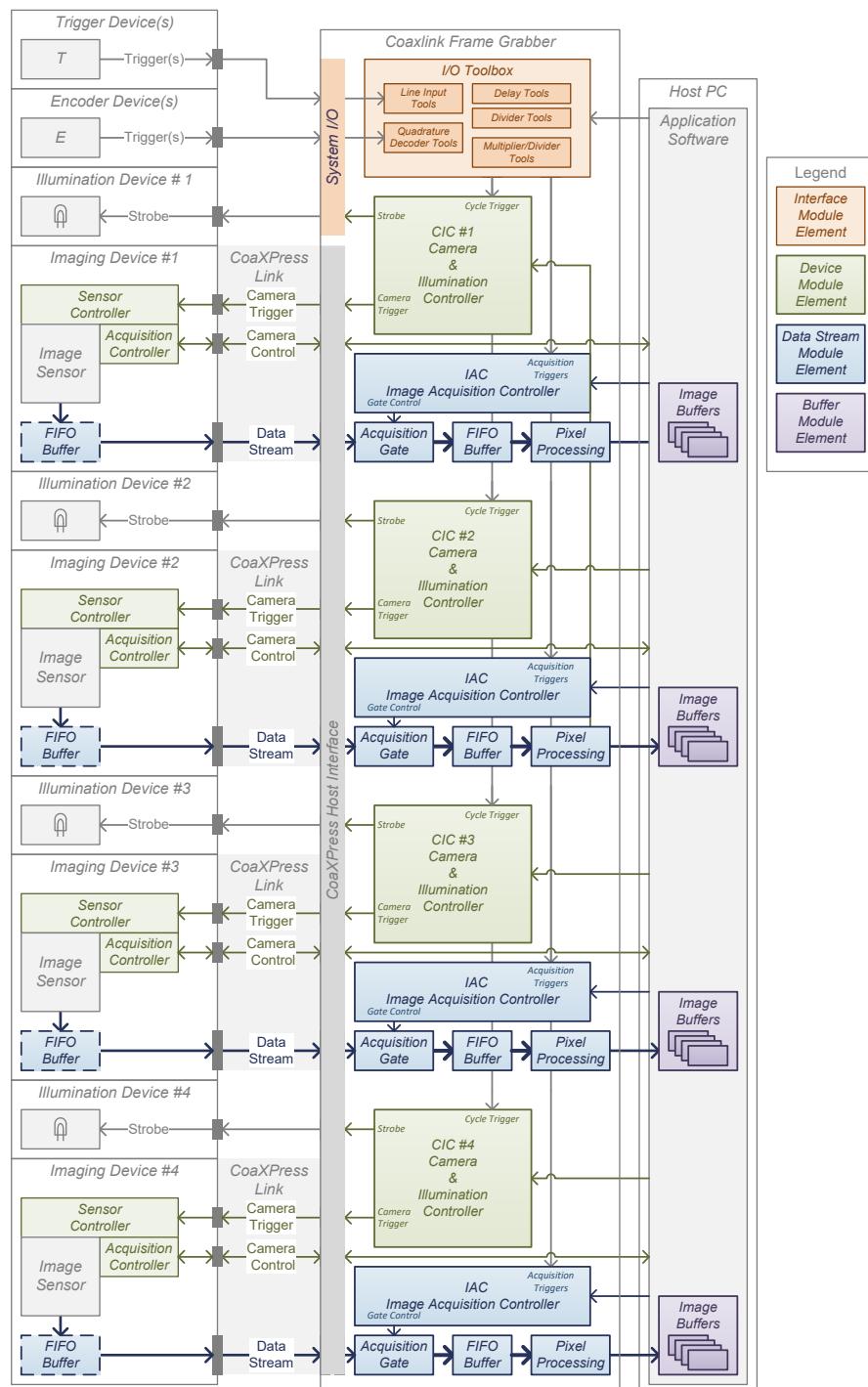

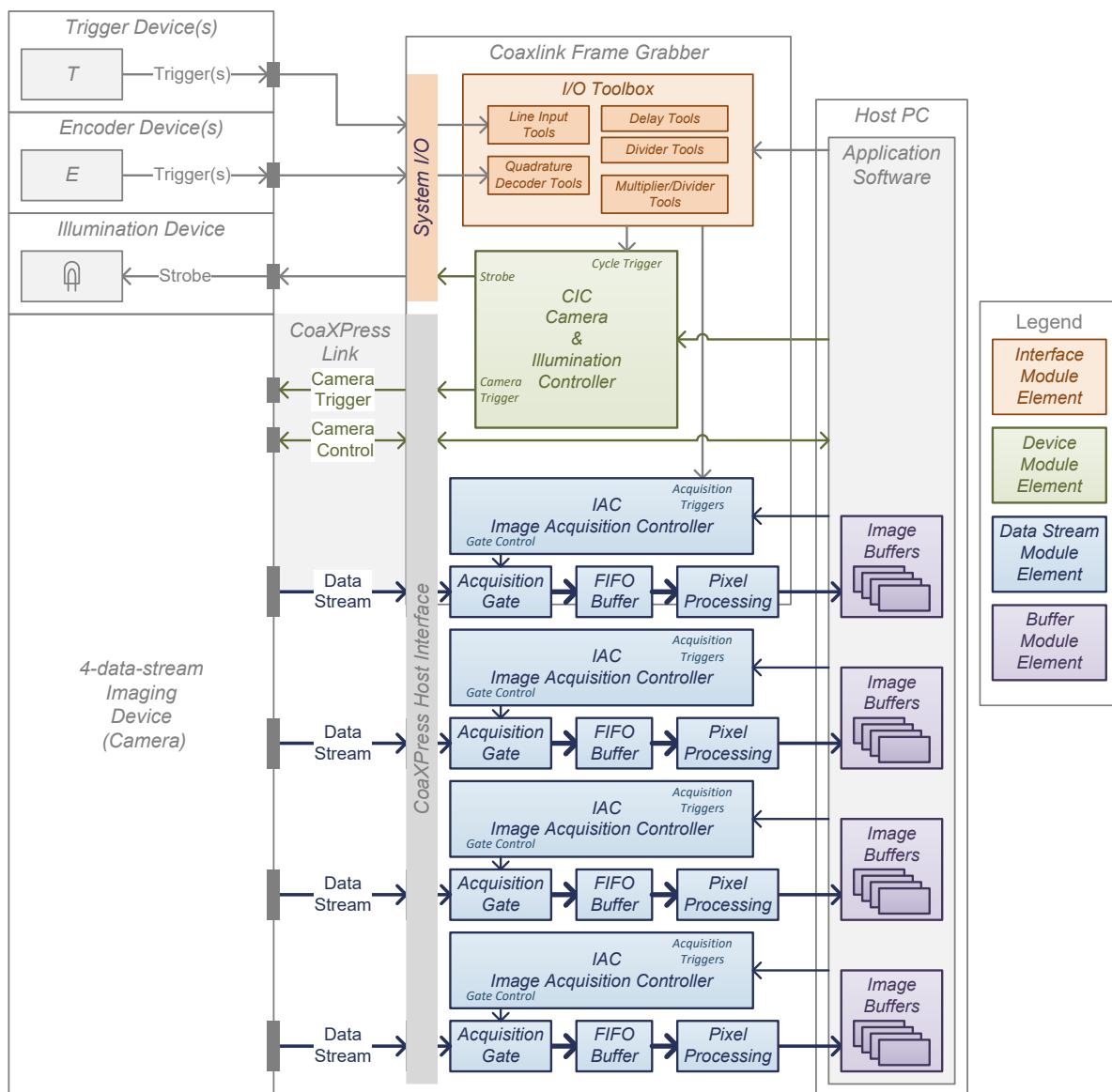

## 1.2. Block Diagrams

### NOTE

In the diagrams hereafter, the main elements are represented by rectangles and their relations are represented by line segments with arrows indicating the direction of the signal or the data flow. The filling color of the rectangle indicates the level in the GenTL hierarchy as described in the legend.

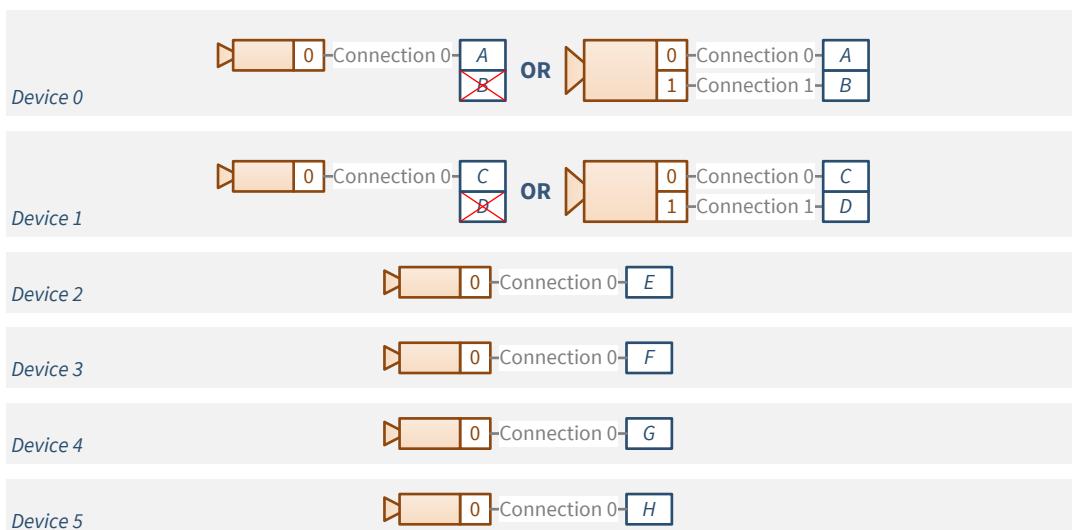

### 1-camera, 1-data-stream

1-camera, 1-data-stream image acquisition system

### NOTE

this configuration applies only when a *1-camera* or a *1-camera, line-scan* firmware variant is installed.

## 2-camera, 1-data-stream

2-camera, 1-data-stream image acquisition system

**NOTE**

this configuration applies only when a 2-camera or a 2-camera, line-scan firmware variant is installed.

## 4-camera, 1-data-stream

4-camera, 1-data-stream image acquisition system

**NOTE**

this configuration applies only when a **4-camera** or a **4-camera, line-scan** firmware variant is installed.

## 1-camera, 4-data-stream

1-camera, 4-data-stream image acquisition system

**NOTE**

this configuration applies only when a **1-camera,4-data-stream** firmware variant is installed.

## 2. CoaXPress Host Interface

|                                                      |    |

|------------------------------------------------------|----|

| 2.1. CoaXPress Interface Specifications .....        | 38 |

| 2.2. Host Connections Maps for Coaxlink Series ..... | 41 |

| 2.3. CoaXPress Link Configuration .....              | 51 |

| 2.4. Power Over CoaXPress .....                      | 52 |

| 2.5. CoaXPress I/O Channel .....                     | 55 |

| 2.6. CoaXPress Host To Device Trigger .....          | 56 |

| 2.7. Advanced Trigger Transmitter Settings .....     | 58 |

| 2.8. Camera Trigger Jitter Compensation .....        | 60 |

| 2.9. Trigger Delay Model .....                       | 63 |

| 2.10. CoaXPress LED Lamps .....                      | 66 |

| 2.11. Connection Test .....                          | 68 |

| 2.12. CoaXPress 2.0 Error Counters .....             | 69 |

| 2.13. CoaXPress Link Validation Tool .....           | 71 |

| 2.14. Multi-tap CoaXPress Cameras .....              | 77 |

## 2.1. CoaXPress Interface Specifications

*Functional specifications summary of the CoaXPress camera interface*

**See also:** "Camera Interfaces" on page 328 in the hardware manual for electrical specifications.

### Connectivity requirements

#### Physical medium and speed range

| Medium                                 | Availability                                      |

|----------------------------------------|---------------------------------------------------|

| Speed range                            |                                                   |

| Coaxial (Copper)<br>CXP-1 up to CXP-6  | QuadG3 Prelim<br>Octo Prelim                      |

| Coaxial (Copper)<br>CXP-1 up to CXP-12 | Mono12LH Prelim<br>Duo12 Prelim<br>Value12 Prelim |

| QSFP+ (Fiber)<br>CXP-1 up to CXP-12    |                                                   |

#### Device count, connection count

The Host Interface of **Coaxlink frame grabbers** requires a specific assignment of the Device connections to the Host connectors. Such assignment is named *Host Connections Map*.

The Host Connections Map is hard-coded in the product firmware variant.

**NOTE:** The Coaxlink frame grabber and the firmware variant must be selected according to the required mapping!

**See also:** "Host Connections Maps for Coaxlink Series" on page 41

#### Data stream count

| Stream count | Availability                            |

|--------------|-----------------------------------------|

| 1 up to 4    | QuadG3 Prelim (1-camera, 4-data-stream) |

| 1            | Other firmware variants                 |

#### Image format requirements

#### Stream packets

| Packet size        | Applicable products |

|--------------------|---------------------|

| Up to 16,384 Bytes | All products        |

## Supported pixel formats

| Pixel Format (PFNC name)                                                                                                                                                                                                       | Usage                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Mono8, Mono10, Mono12, Mono14, Mono16                                                                                                                                                                                          | Monochrome cameras<br>8-/10-/12-/14-/16-bit per pixel                          |

| BayerGR8, BayerRG8, BayerGB8, BayerBG8<br>BayerGR10, BayerRG10, BayerGB10, BayerBG10<br>BayerGR12, BayerRG12, BayerGB12, BayerBG12<br>BayerGR14, BayerRG14, BayerGB14, BayerBG14<br>BayerGR16, BayerRG16, BayerGB16, BayerBG16 | Bayer CFA color cameras<br>8-/10-/12-/14-/16-bit per pixel component           |

| RGB8, RGB10, RGB12, RGB14, RGB16                                                                                                                                                                                               | Three-component RGB color cameras<br>8-/10-/12-/14-/16-bit per pixel component |

| RGBA8, RGBA10, RGBA12, RGBA14, RGBA16                                                                                                                                                                                          | Four-component RGBI color cameras<br>8-/10-/12-/14-/16-bit per pixel component |

| Raw                                                                                                                                                                                                                            | Undefined format                                                               |

## Image stream format

| Stream format                  | Availability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acquisition                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Rectangular image<br>Area-scan | <p> <b>QuadG3</b> (1-camera), (1-camera, 4-data-stream), (2-camera), (2-camera, bayer), (3-camera), (4-camera)</p> <p> <b>Octo</b> (1-camera), (1-camera, custom-logic), (2-camera), (3-camera), (4-camera), (5-camera), (5-camera, 5D22211), (6-camera), (8-camera)</p> <p> <b>Mono1ZLH</b> (1-camera)</p> <p> <b>Duo1Z</b> (1-camera), (2-camera)</p> <p> <b>Value1Z</b> (1-camera), (2-camera), (3-camera), (4-camera)</p>                            |

| Rectangular image<br>Line-scan | <p> <b>QuadG3</b> (1-camera, line-scan), (2-camera, line-scan), (4-camera, line-scan)</p> <p> <b>Octo</b> (1-camera, line-scan), (2-camera, line-scan), (2-camera, line-scan, custom-logic), (4-camera, line-scan), (8-camera, line-scan)</p> <p> <b>Mono1ZLH</b> (1-camera, line-scan)</p> <p> <b>Duo1Z</b> (1-camera, line-scan), (2-camera, line-scan)</p> <p> <b>Value1Z</b> (1-camera, line-scan), (2-camera, line-scan), (4-camera, line-scan)</p> |

| Arbitrary image                | Not supported                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Supported scanning methods

| Scanning Geometry (Stream)                              | Availability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Progressive-scan 1X_1Y                                  | All firmware variants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Progressive-scan 1X-2YE (Dual stream)                   |  Value1Z (1-camera)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Progressive-scan 1X_1Y2, 1X_2YE, 1X_2YM (Single stream) |  QuadG3 (1-camera), (1-camera, 4-data-stream), (2-camera), (2-camera, bayer), (3-camera), (4-camera)<br> Octo (1-camera), (1-camera, custom-logic), (2-camera), (3-camera), (4-camera), (5-camera), (5-camera, 5D22211), (6-camera), (8-camera)<br> Mono1ZLH (1-camera)<br> Duo1Z (1-camera), (2-camera)<br> Value1Z (1-camera), (2-camera), (3-camera), (4-camera) |

| Interlaced-scan                                         | Not supported                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## 2.2. Host Connections Maps for Coaxlink Series

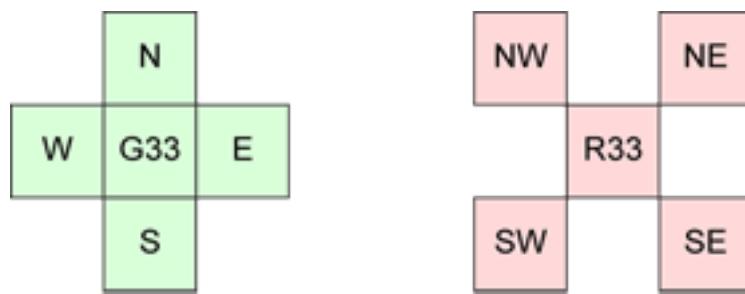

The Host Interface of **Coaxlink frame grabbers** requires a specific assignment of the Device connections to the Host connectors. Such assignment is named *Host Connections Map*.

The Host Connections Map is hard-coded in the product firmware variant.

**NOTE:** The Coaxlink frame grabber and the firmware variant must be selected according to the required mapping!

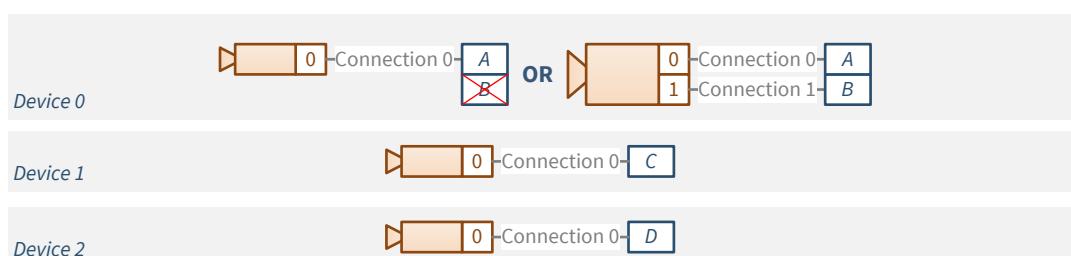

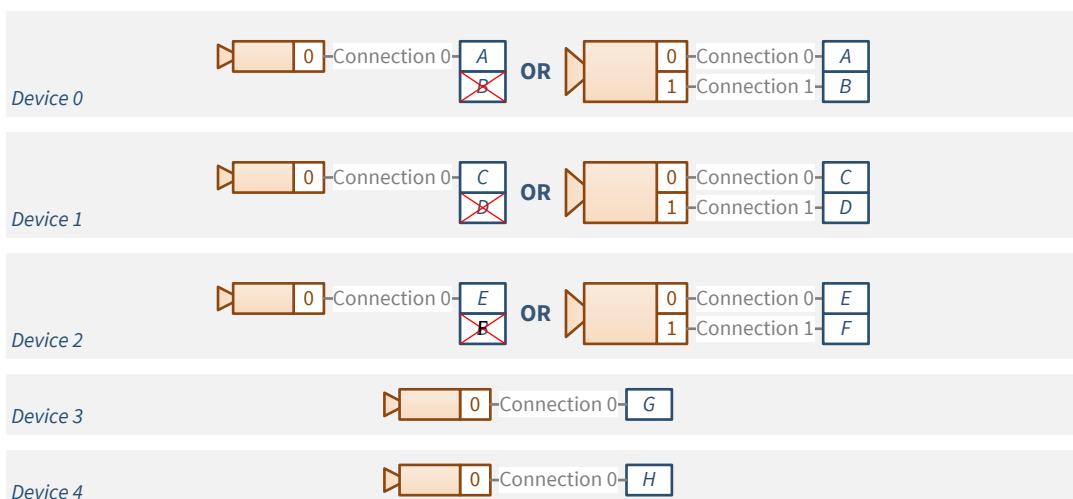

### 1D1 host connections map

Applies to the following firmware variants of **PC3621-LH-T Coaxlink Mono CXP-12-LH**:

**Mono1ZLH** (1-camera), (1-camera, line-scan)

One 1-connection device

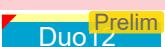

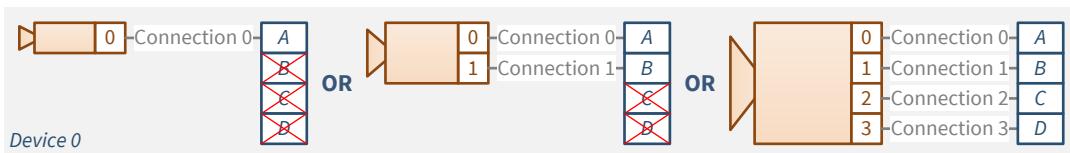

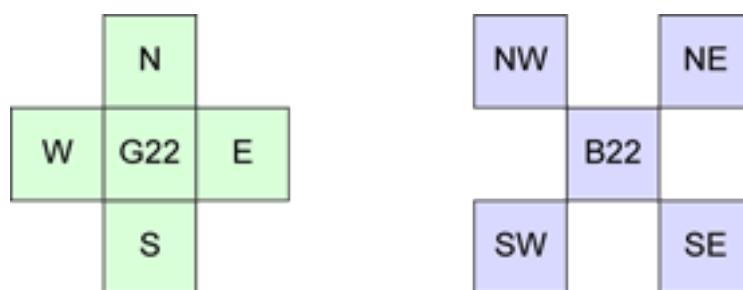

### 1D2 host connections map

Applies to the following firmware variants of **PC3622-T Coaxlink Duo CXP-12**:

**Duo1Z** (1-camera), (1-camera, line-scan)

One 1- or 2-connection device

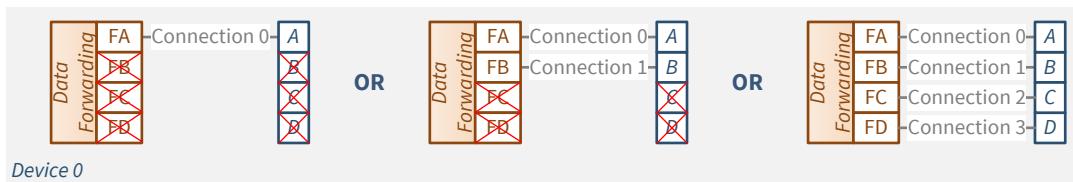

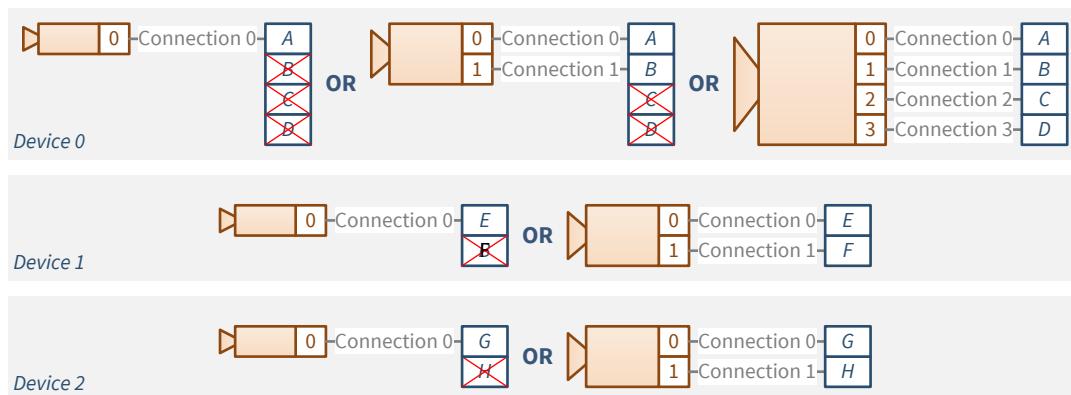

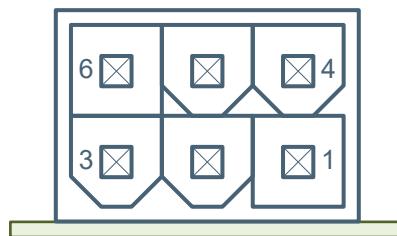

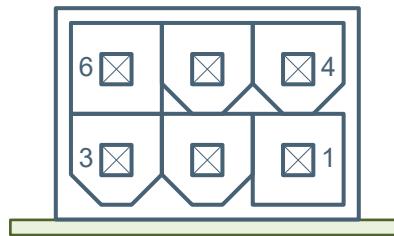

## 1D4 host connections map

Applies to the following firmware variants of **PC1633-T Coaxlink Quad G3**, **PC3602-T Coaxlink Octo** and **PC3623-T Coaxlink Quad CXP-12 Value**:

**QuadG3** <sup>Prelim</sup> (1-camera), (1-camera, 4-data-stream), (1-camera, line-scan)

**Octo** <sup>Prelim</sup> (1-camera, custom-logic)

**Value12** <sup>Prelim</sup> (1-camera), (1-camera, line-scan)

One 1- or 2- or 4-connection device

## 1D4S4 host connections map

Applies to the following firmware variants of **PC1633-T Coaxlink Quad G3**, **PC3602-T Coaxlink Octo** and **PC3623-T Coaxlink Quad CXP-12 Value**:

**QuadG3** <sup>Prelim</sup> (1-camera), (1-camera, 4-data-stream), (1-camera, line-scan)

**Octo** <sup>Prelim</sup> (1-camera, custom-logic)

**Value12** <sup>Prelim</sup> (1-camera), (1-camera, line-scan)

One 1- or 2- or 4-connection device, up to 4 data streams

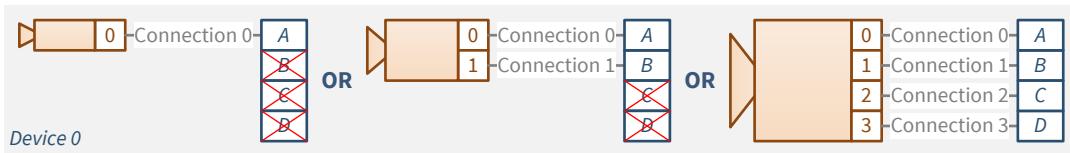

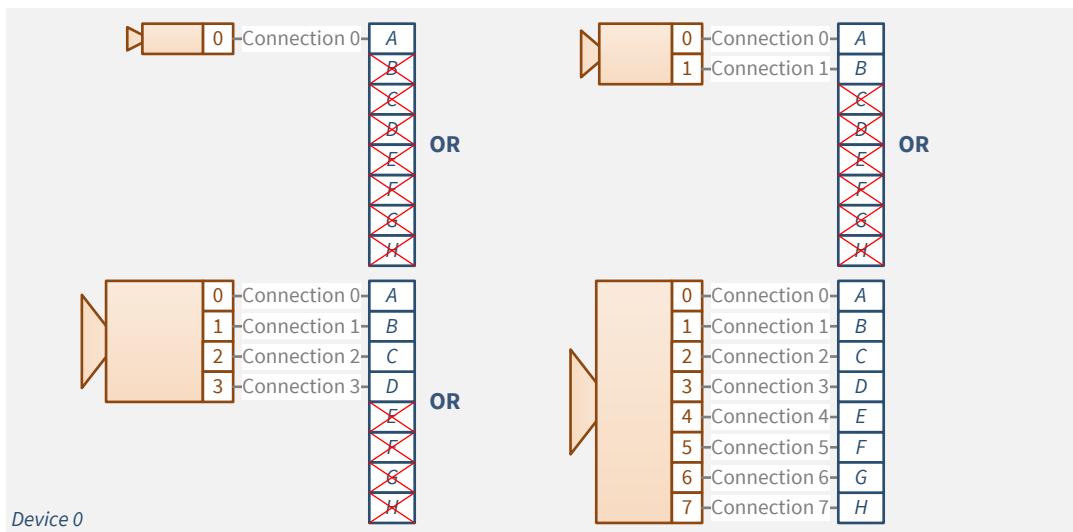

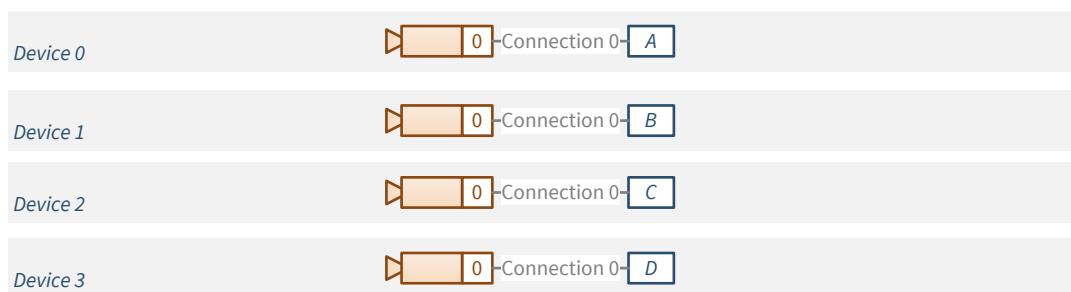

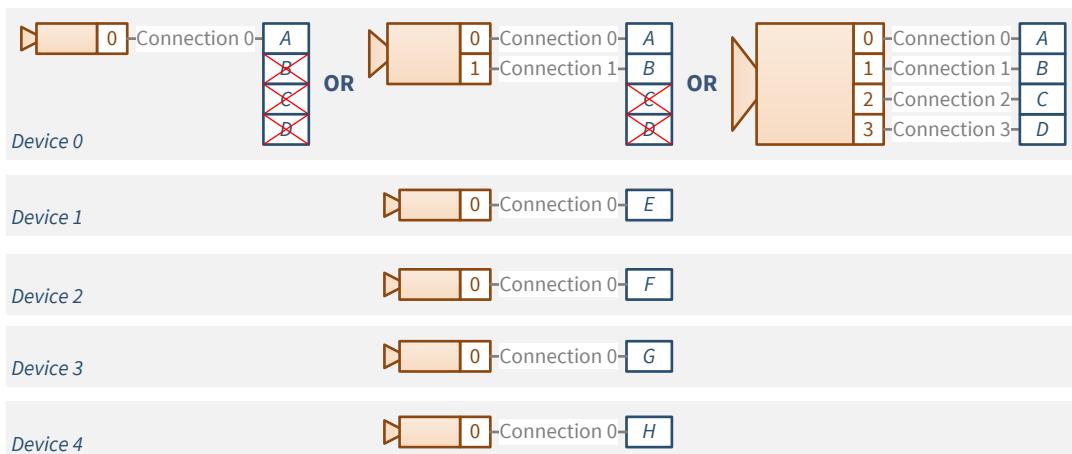

## 1D8 host connections map

Applies to the following firmware variants of PC3602-T Coaxlink Octo:

Octo Prelim (1-camera), (1-camera, line-scan)

One 1- or 2- or 4- or 8-connection device

## 1DF4 host connections map

One 1- or 2- or 4-connection device

See also: CoaXPress Data Forwarding for the connection schemes of slave Data Forwarding devices.

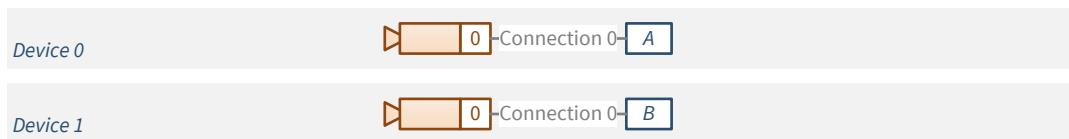

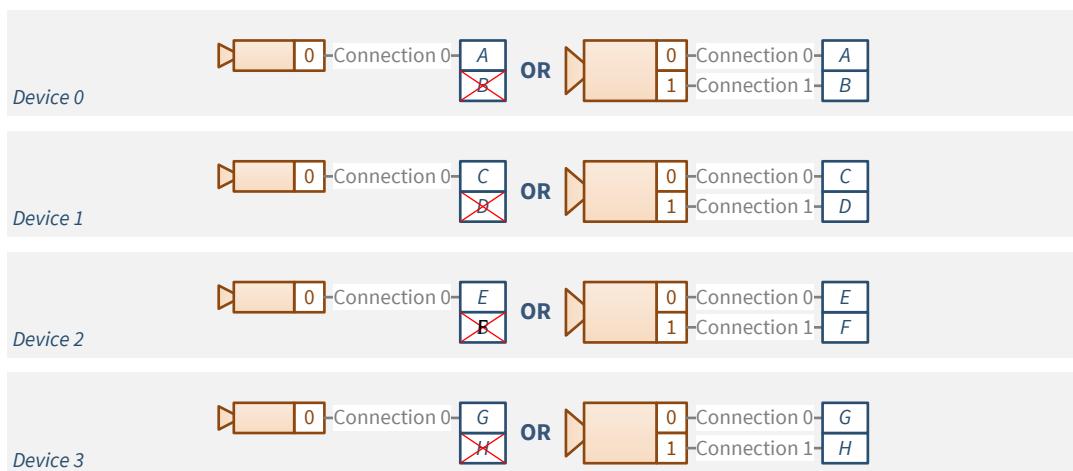

## 2D11 host connections map

Applies to the following firmware variants of **PC3622-T Coaxlink Duo CXP-12**:

**Duo12** (2-camera), (2-camera, line-scan)

One or two 1-connection devices

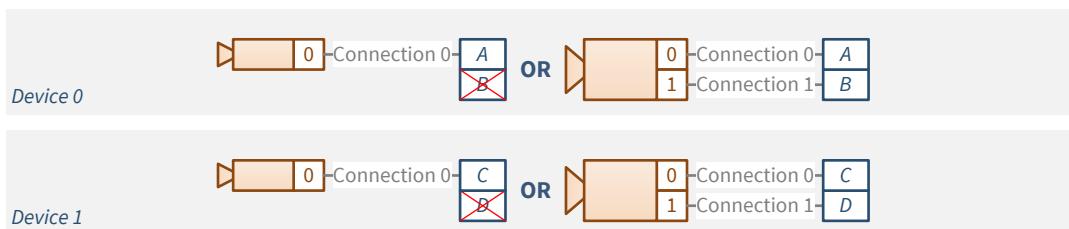

## 2D22 host connections map

Applies to the following firmware variants of **PC1633-T Coaxlink Quad G3** and **PC3623-T Coaxlink Quad CXP-12 Value**:

**QuadG3** (2-camera), (2-camera, bayer), (2-camera, line-scan)

**Value12** (2-camera), (2-camera, line-scan)

One or two 1- or 2-connection devices

## 2D44 host connections map

Applies to the following firmware variants of PC3602-T Coaxlink Octo:

(2-camera), (2-camera, line-scan), (2-camera, line-scan, custom-logic)

One or two 1- or 2- or 4-connection devices

## 3D211 host connections map

Applies to the following firmware variants of PC1633-T Coaxlink Quad G3 and PC3623-T Coaxlink Quad CXP-12 Value:

(3-camera)

(3-camera)

One 1- or 2-connection and one or two 1-connection devices

## 3D422 host connections map

Applies to the following firmware variants of PC3602-T Coaxlink Octo:

Octo (3-camera)

One 1- or 2- or 4-connection and one or two 1- or 2-connection devices

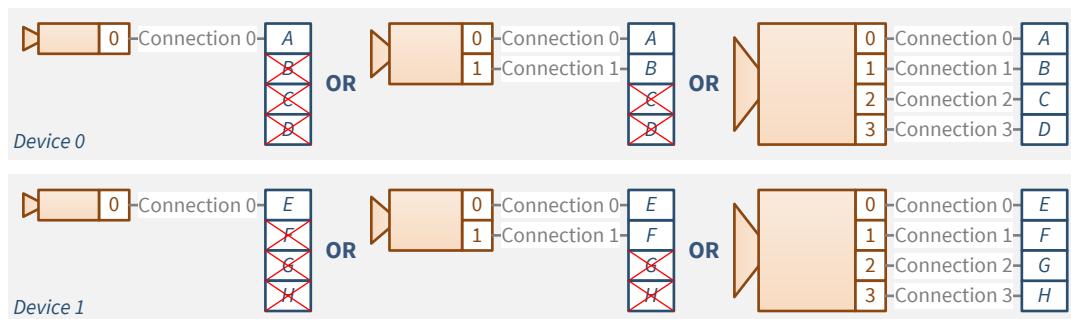

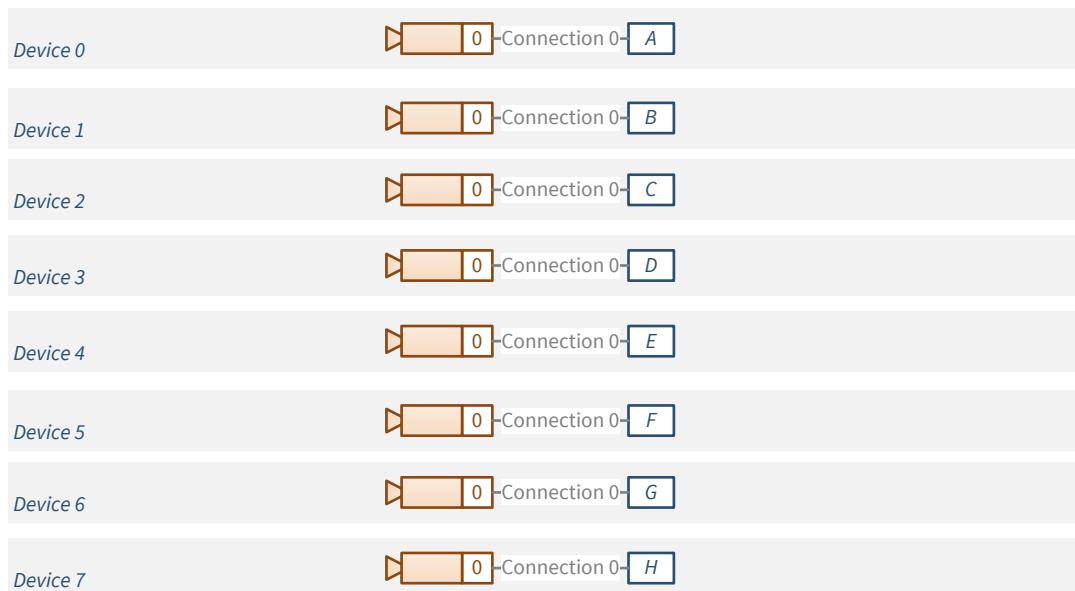

## 4D1111 host connections map

Applies to the following firmware variants of PC1633-T Coaxlink Quad G3 and PC3623-T Coaxlink Quad CXP-12 Value:

QuadG3 (4-camera), (4-camera, line-scan)

Value12 (4-camera), (4-camera, line-scan)

One or two or three or four 1-connection devices

## 4D2222 host connections map

Applies to the following firmware variants of PC3602-T Coaxlink Octo:

Octo Prelim (4-camera), (4-camera, line-scan)

One or two or three or four 1- or 2-connection devices

## 5D22211 host connections map

Applies to the following firmware variants of PC3602-T Coaxlink Octo:

Octo Prelim (5-camera, 5D22211)

One or two or three 1- or 2-connection and one or two 1-connection devices

## 5D41111 host connections map

Applies to the following firmware variants of PC3602-T Coaxlink Octo:

(5-camera)

One 1- or 2- or 4-connection and one or two or three or four 1-connection devices

## 6D221111 host connections map

Applies to the following firmware variants of PC3602-T Coaxlink Octo:

(6-camera)

One or two 1- or 2-connection and one or two or three or four 1-connection devices

## 8D11111111 host connections map

Applies to the following firmware variants of PC3602-T Coaxlink Octo:

Octo Prelim (8-camera), (8-camera, line-scan)

Up to eight 1-connection devices

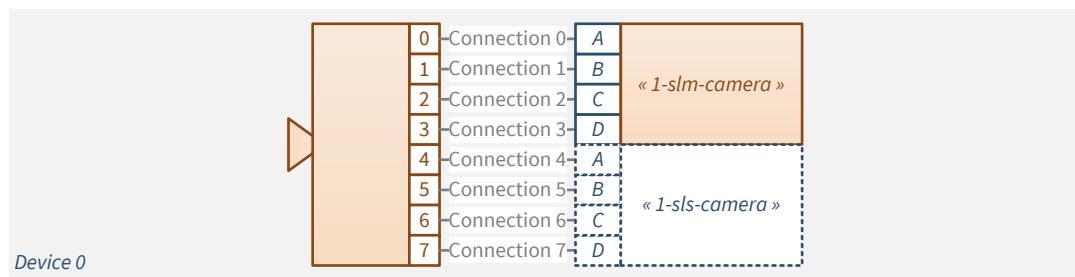

## 1D8SLM4 host connections map

Master 4-connection sub-link of an 8-connection device

See also: 8-connection CoaXPress Cameras for the connection scheme of an 8-connection camera to two Coaxlink cards.

## 1D8SLS4 host connections map

Slave 4-connection sub-link of an 8-connection device

See also: 8-connection CoaXPress Cameras for the connection scheme of an 8-connection camera to two Coaxlink cards.

## 2.3. CoaXPress Link Configuration

### Automatic Link Configuration

---

The **eGrabber** driver provides an automatic link discovery and configuration for CoaXPress 1.0 , CoaXPress 1.1 and CoaXPress 2.0 devices.

For each connection of the CoaXPress Host interface, the discovery procedure determines:

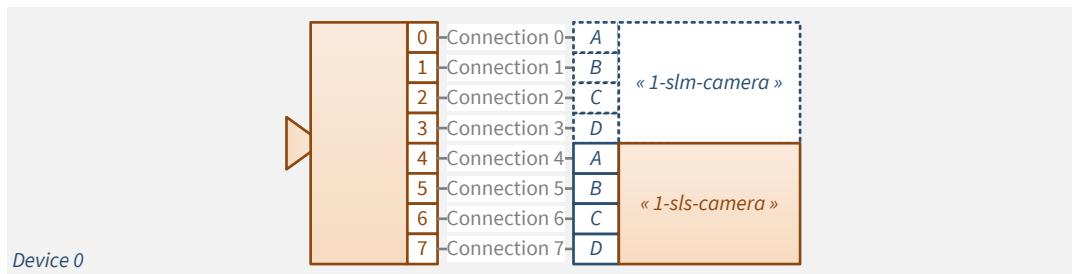

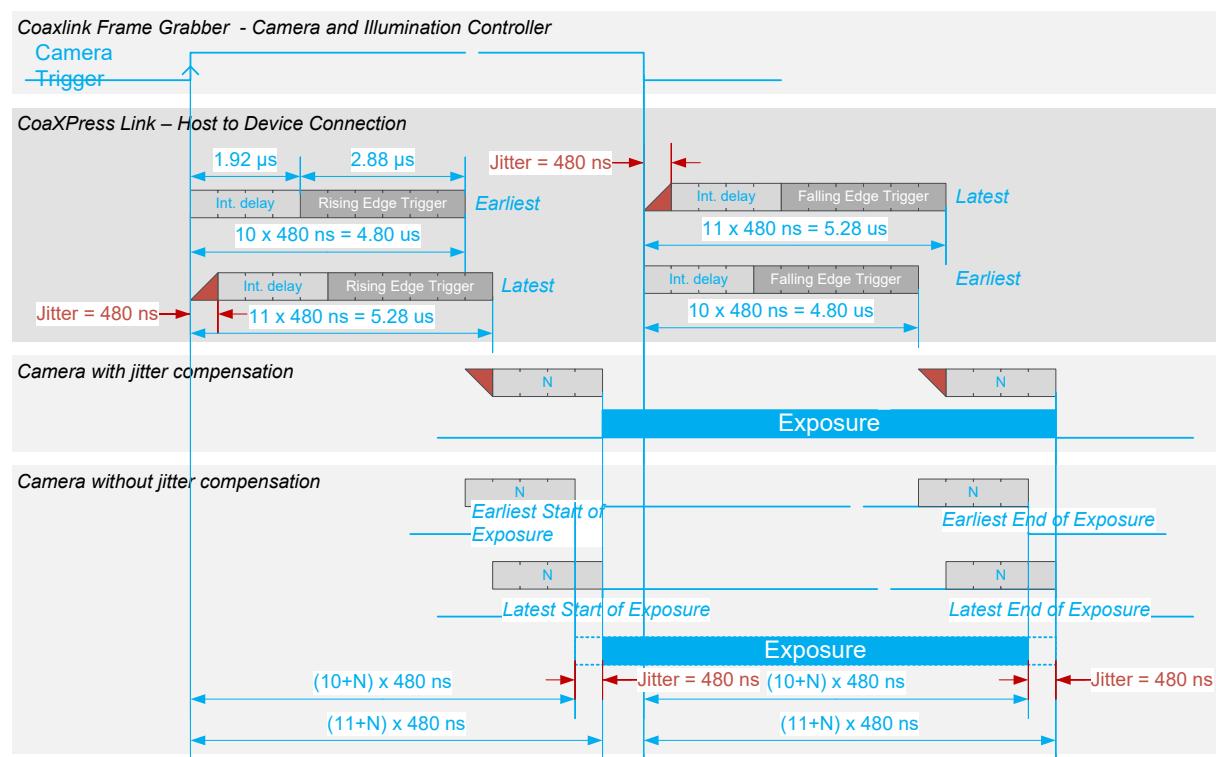

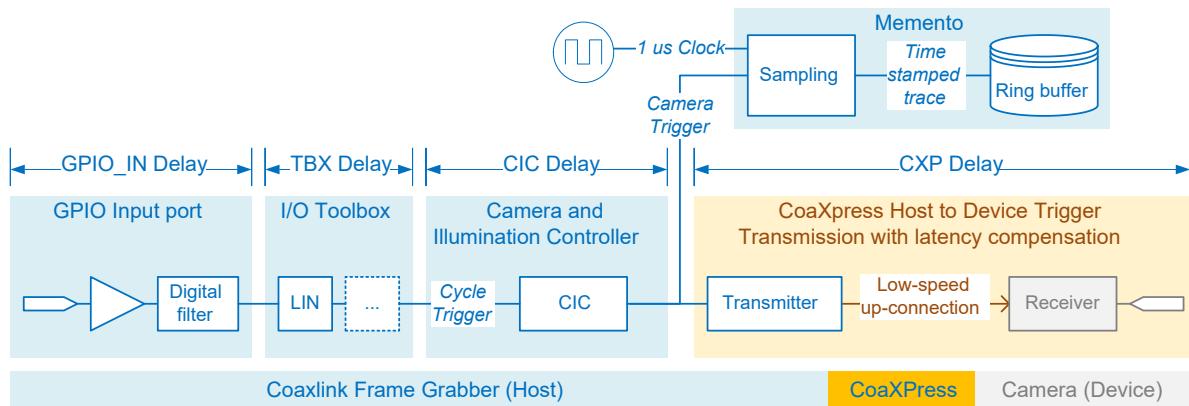

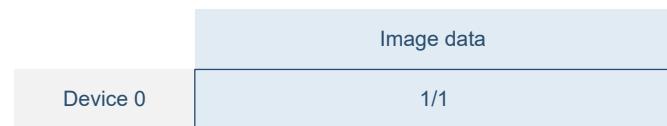

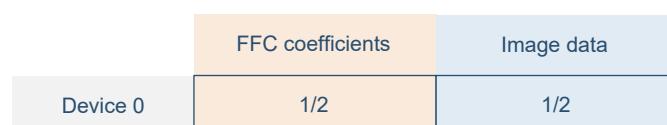

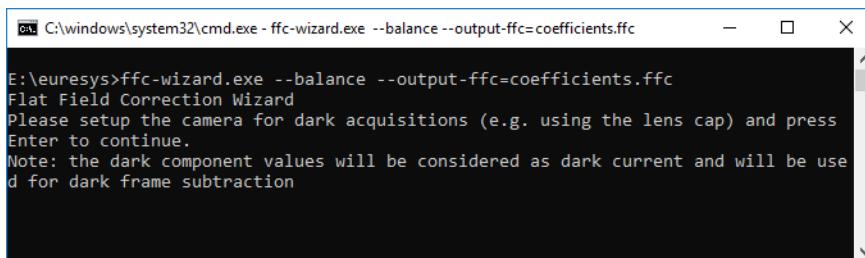

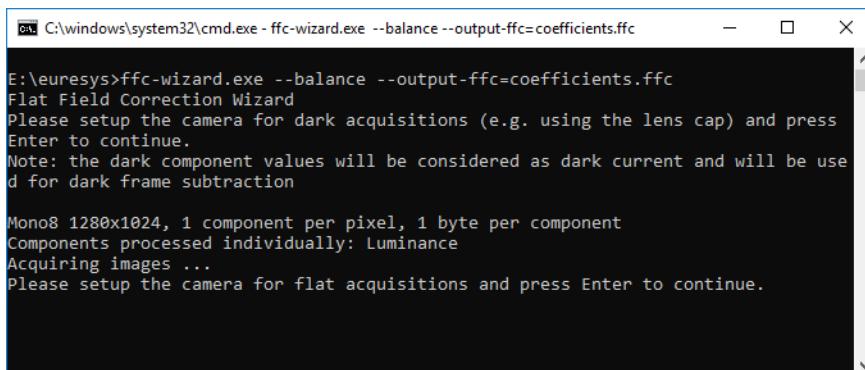

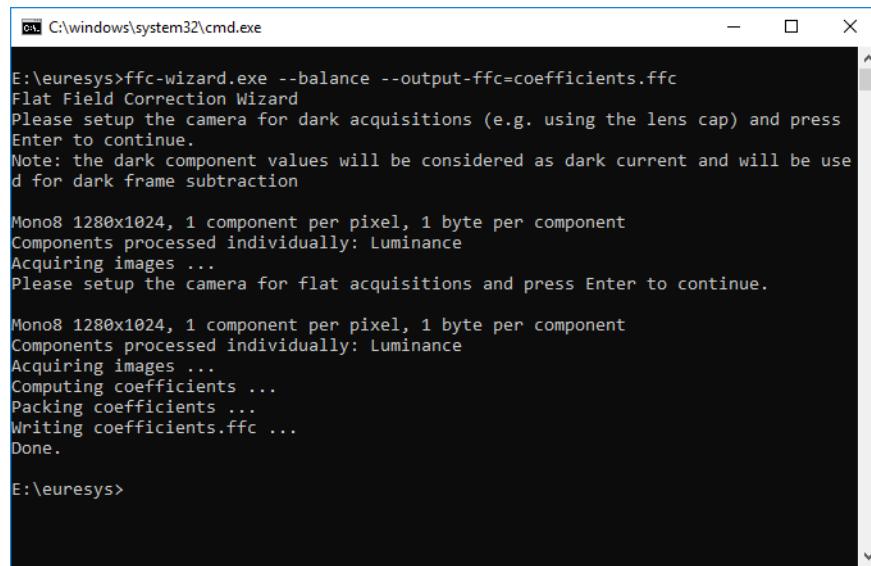

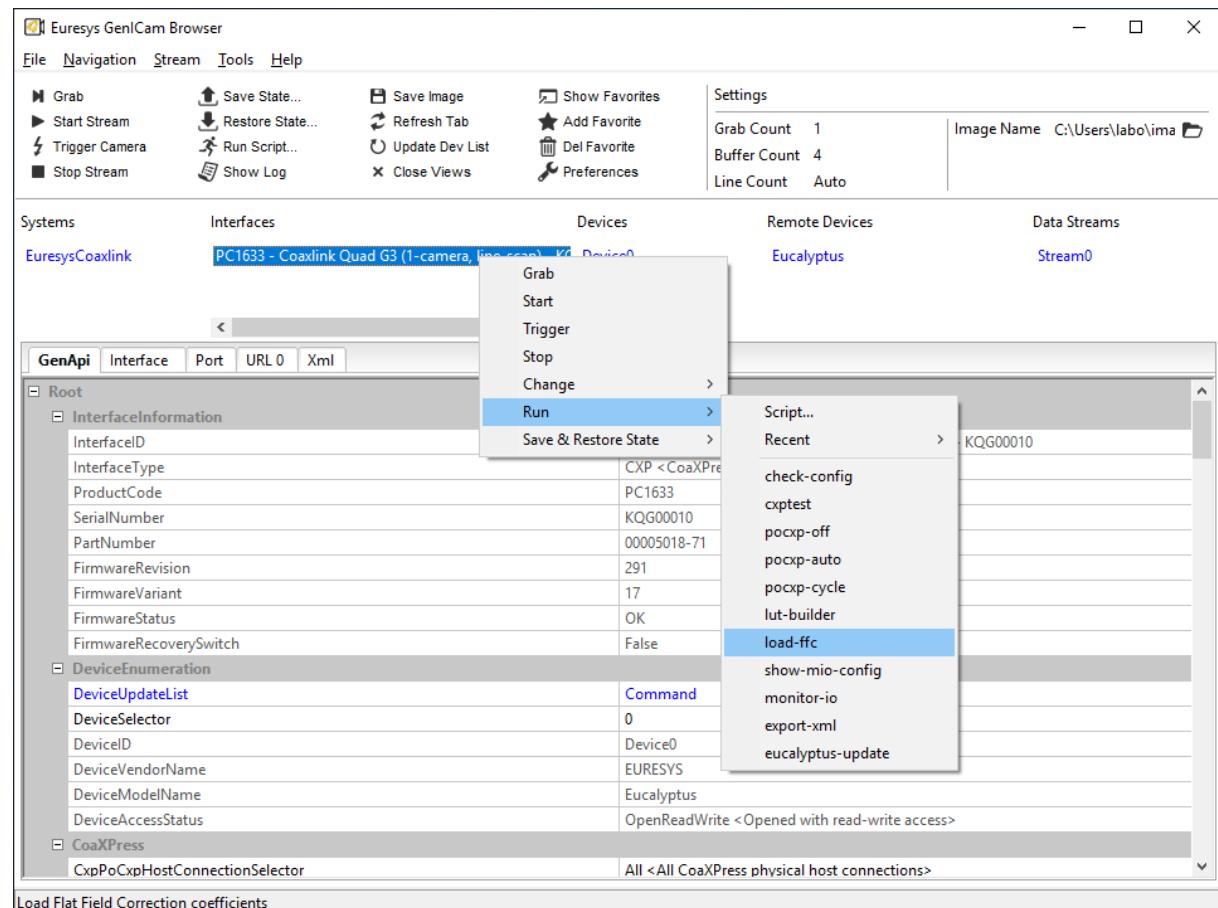

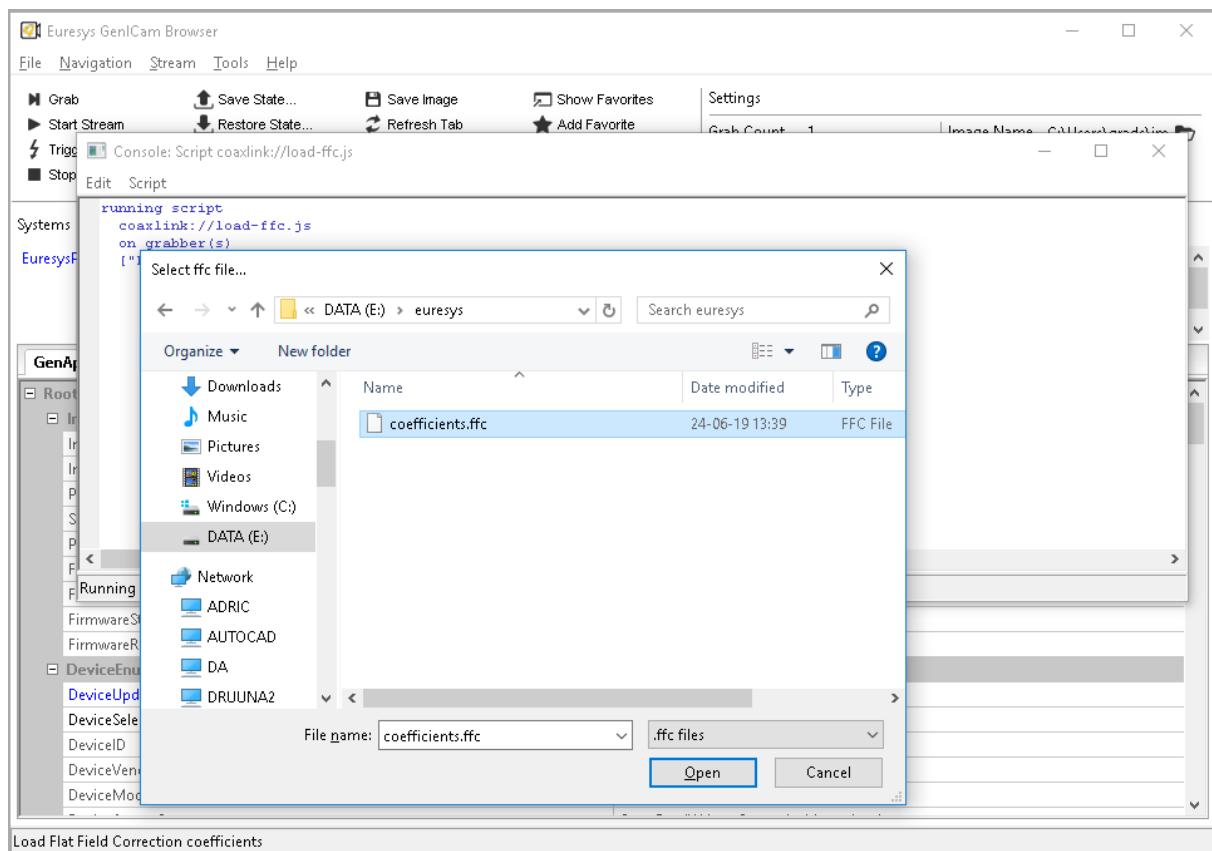

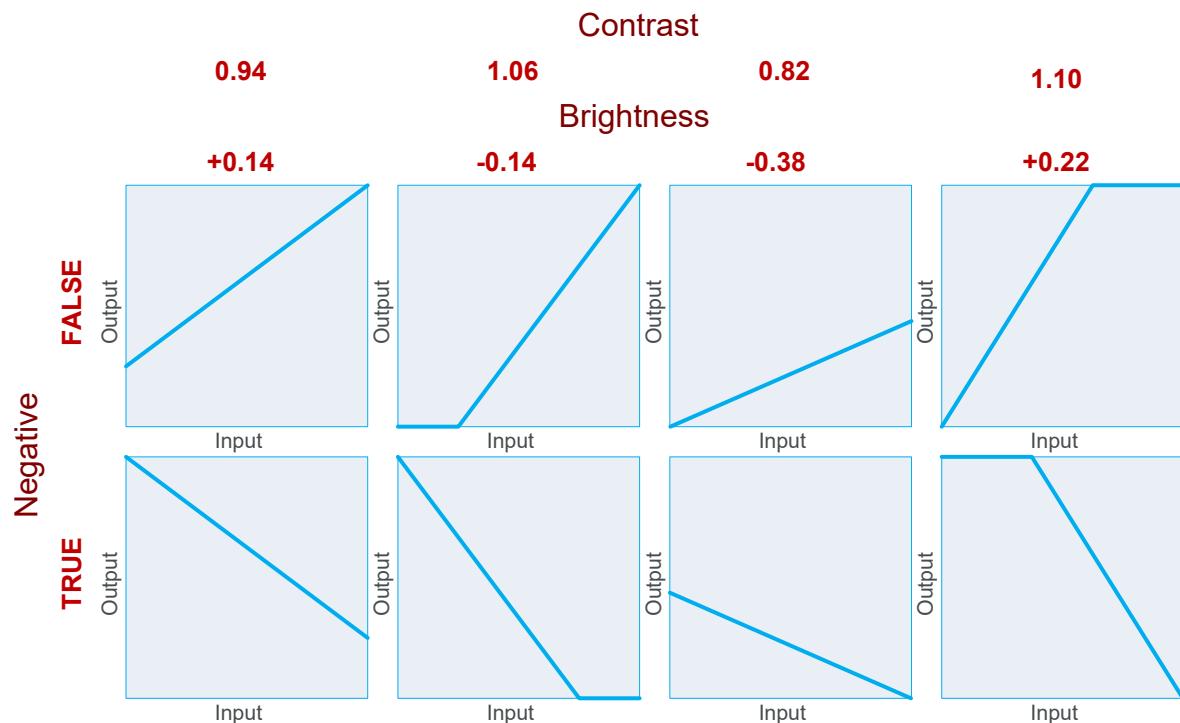

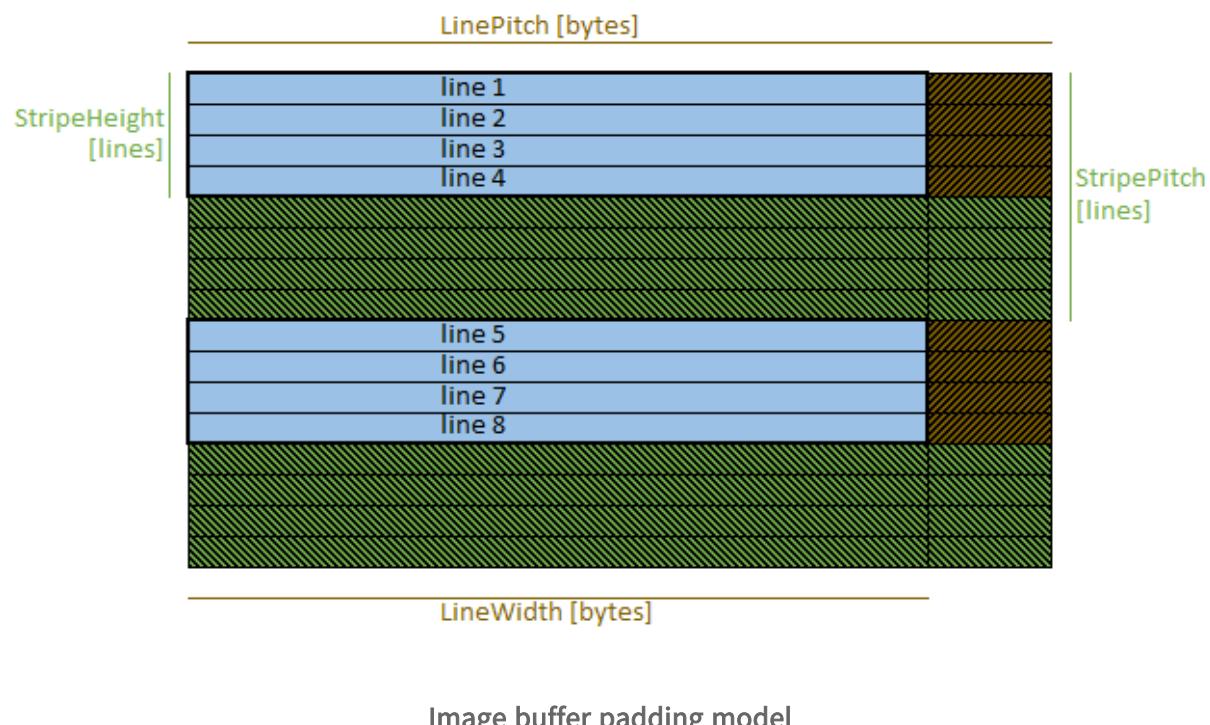

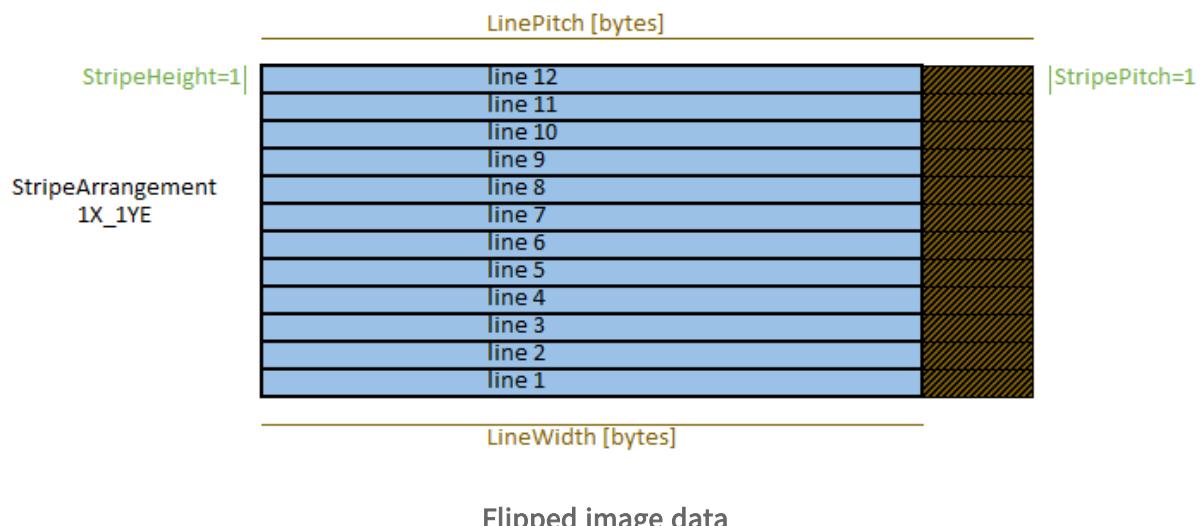

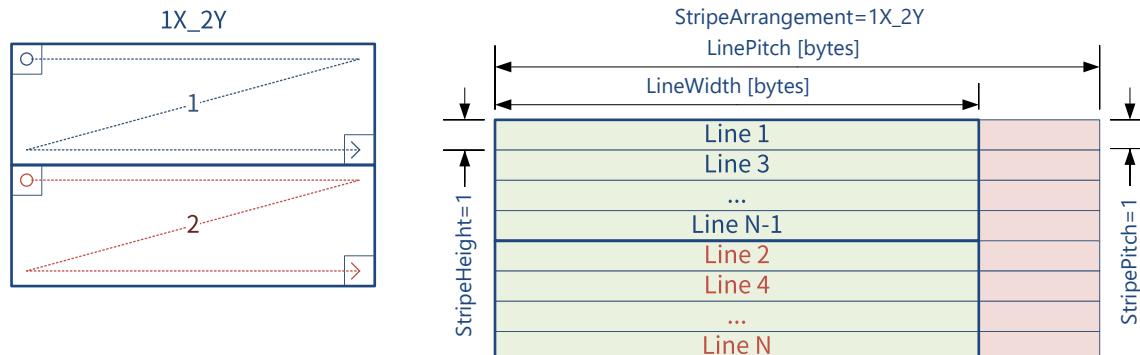

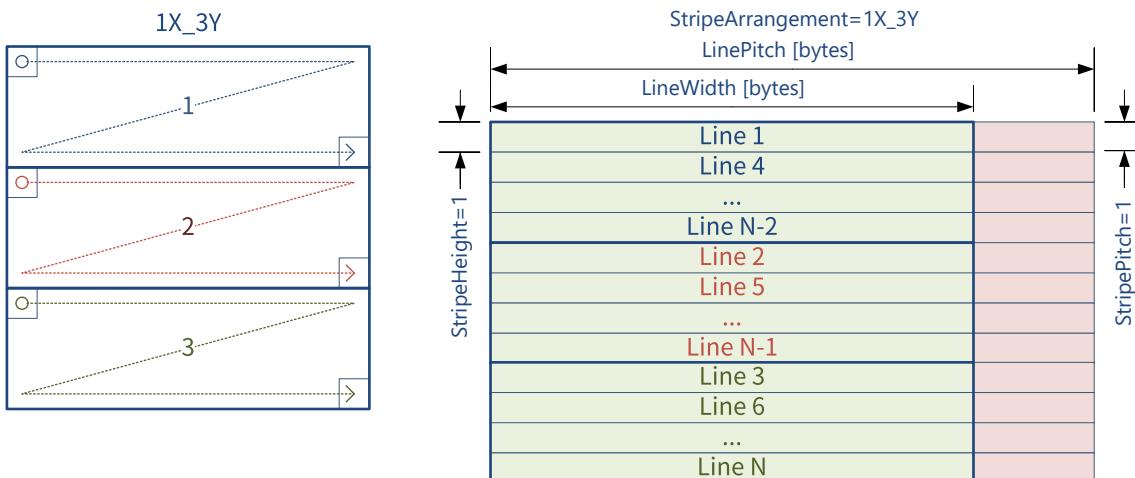

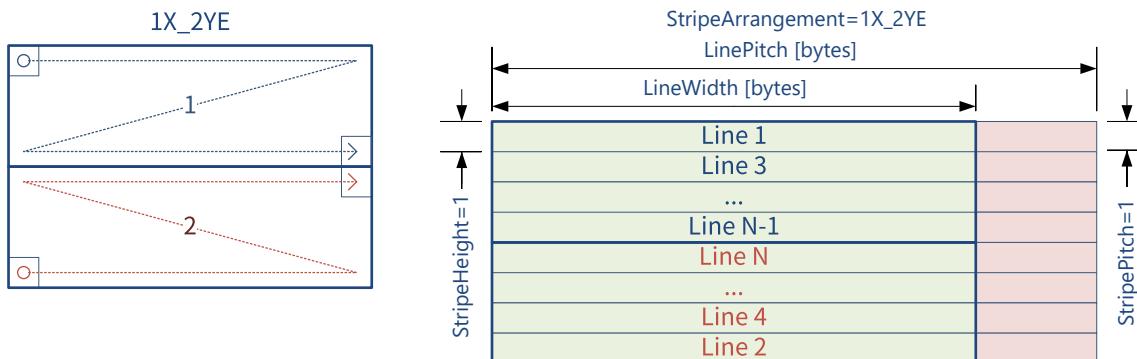

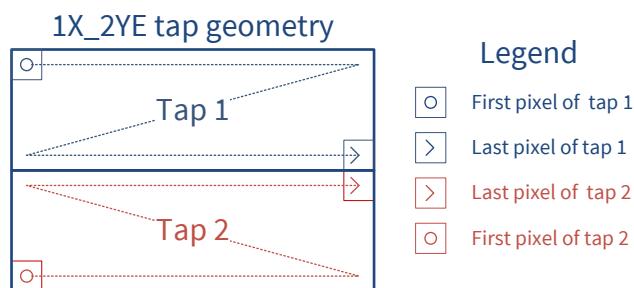

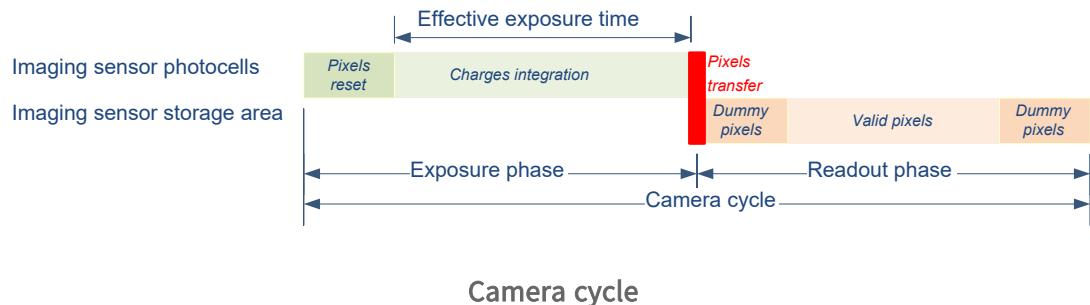

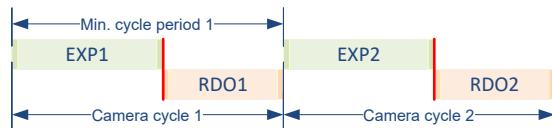

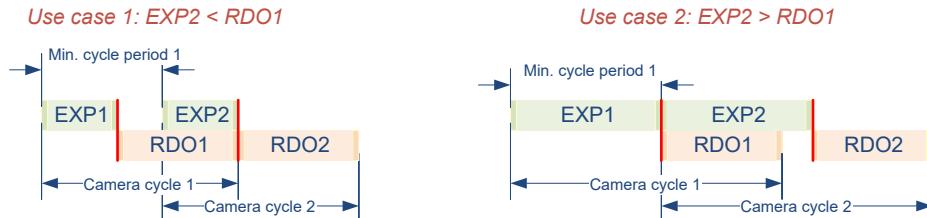

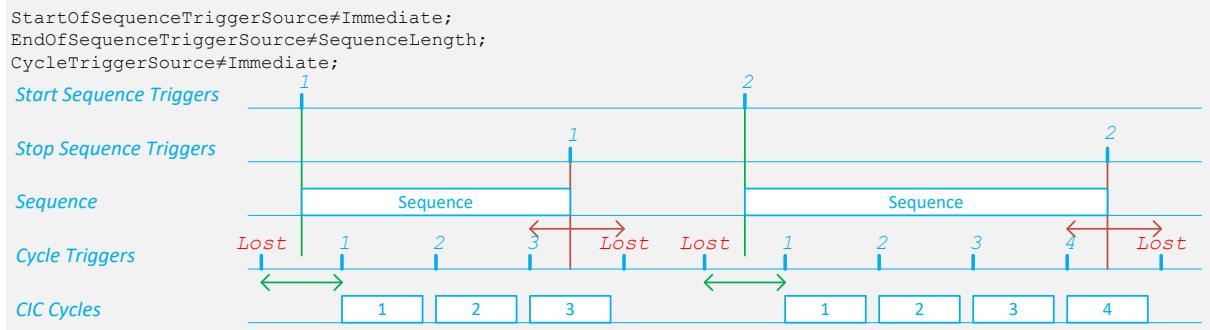

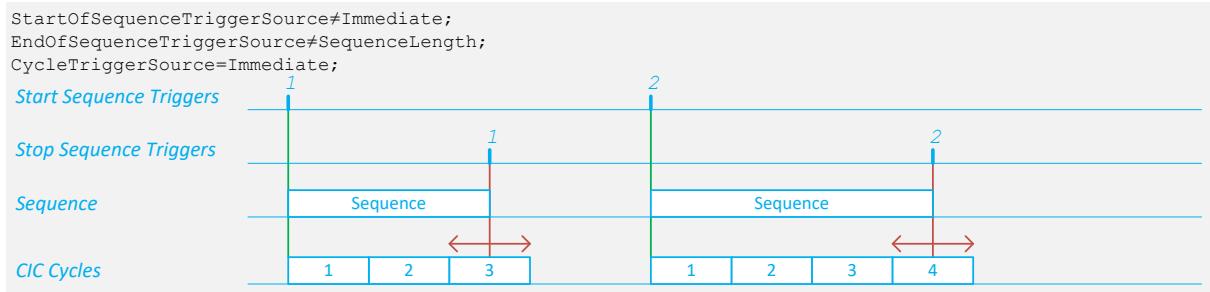

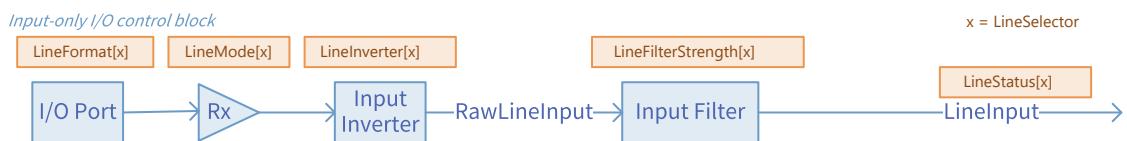

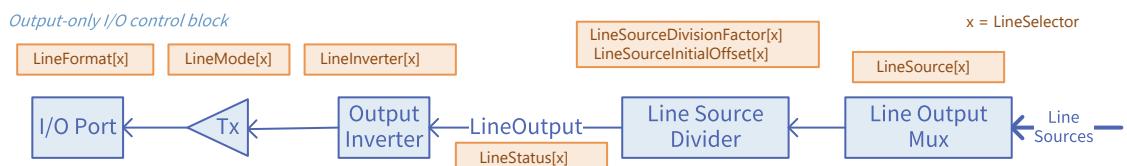

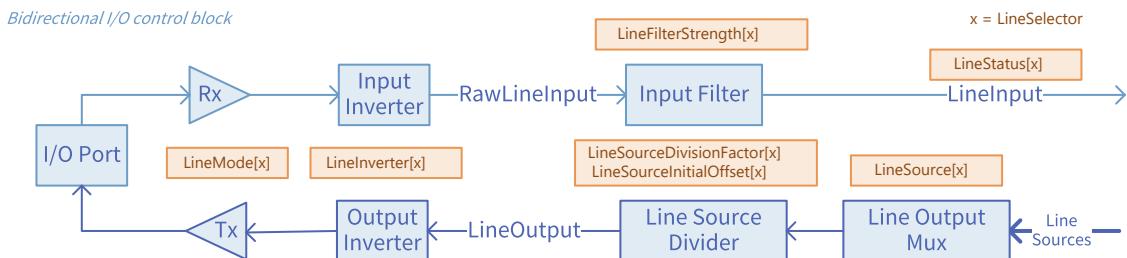

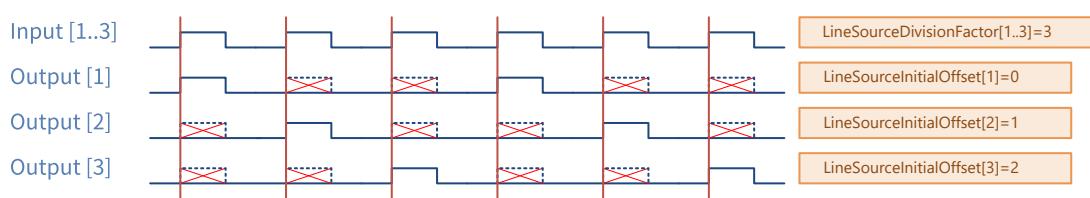

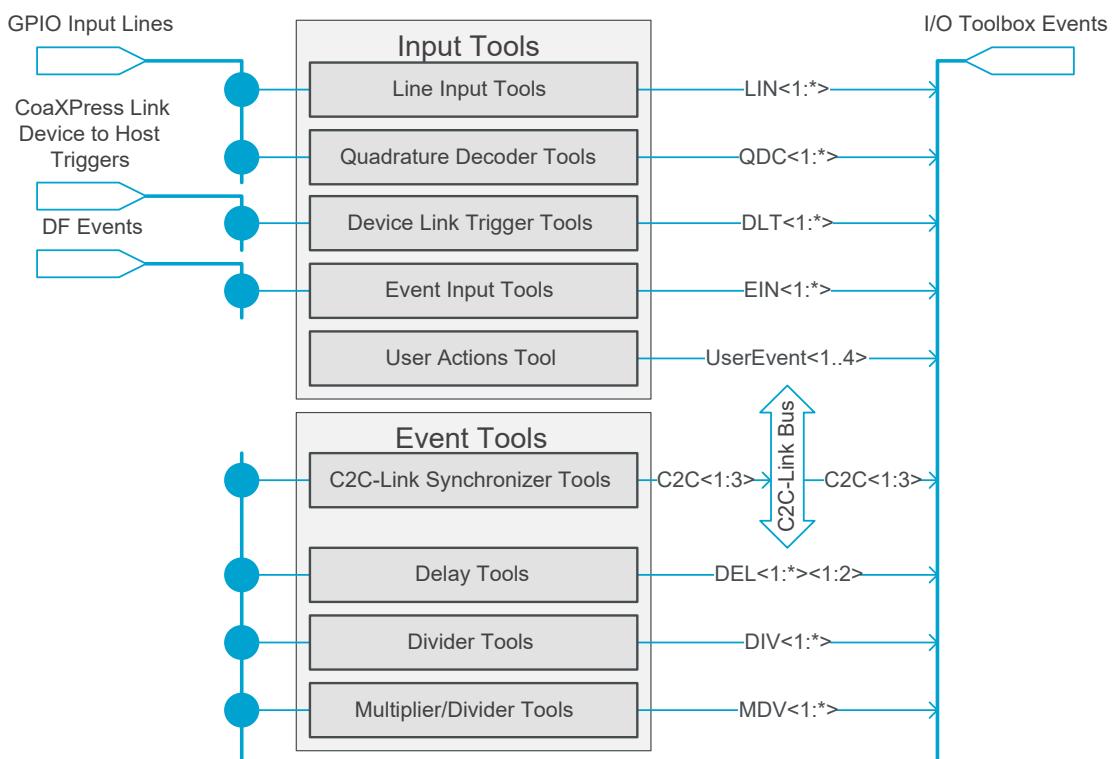

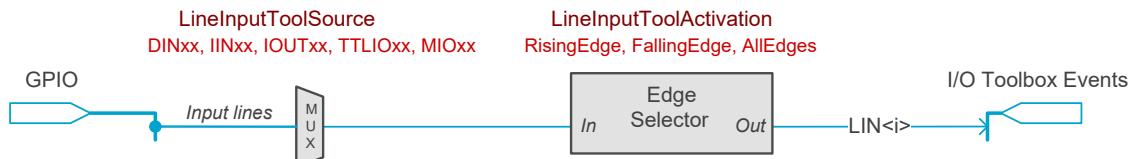

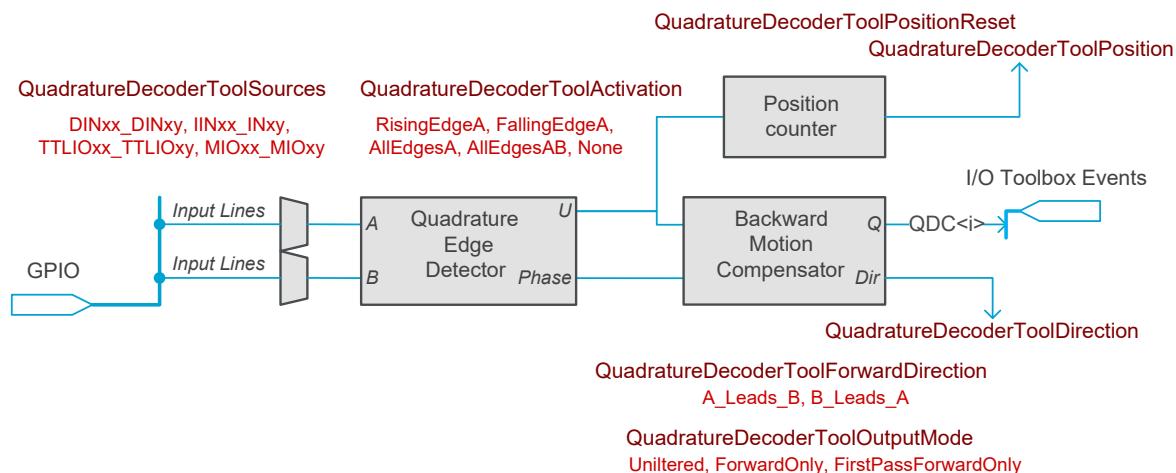

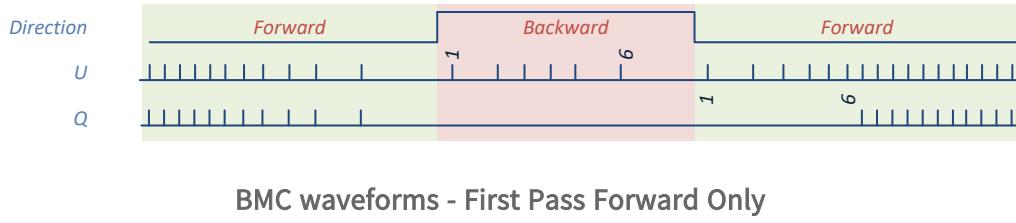

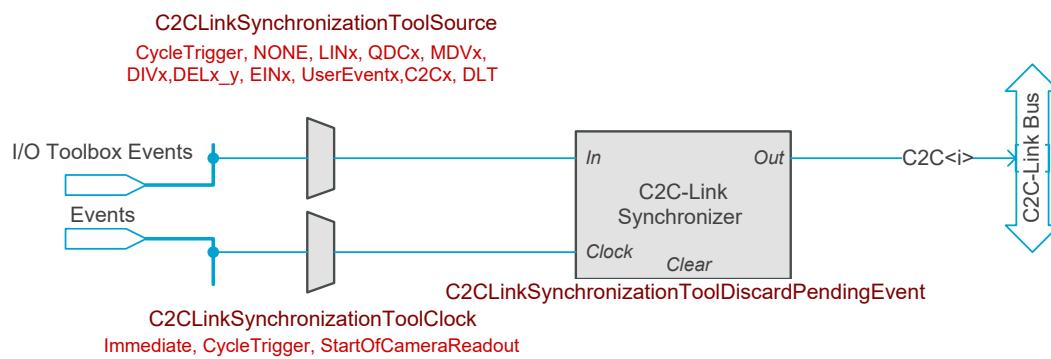

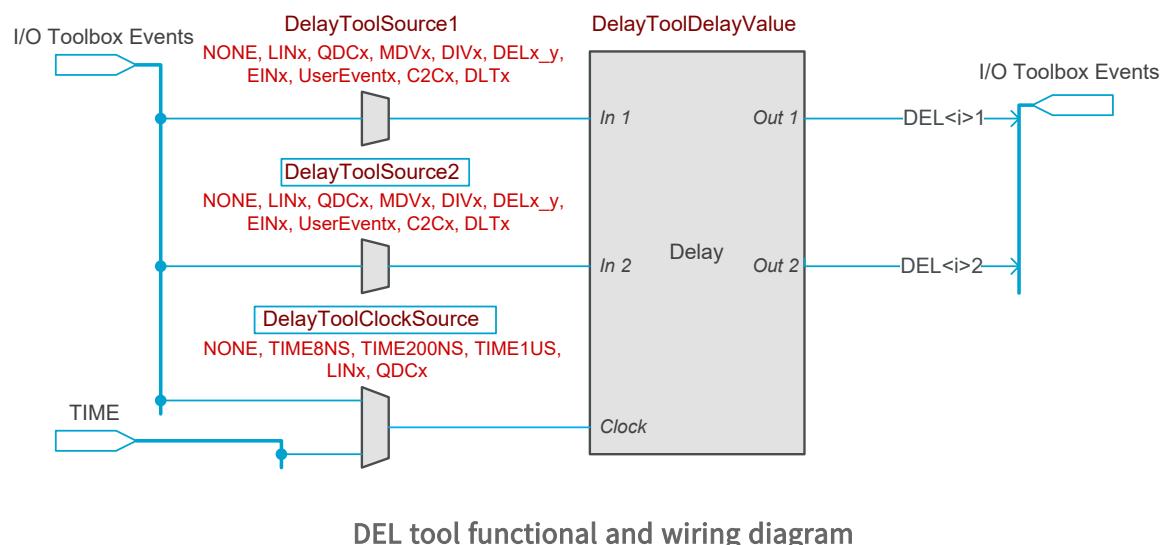

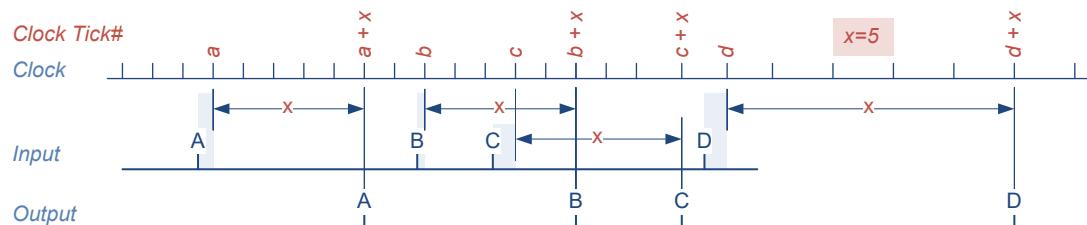

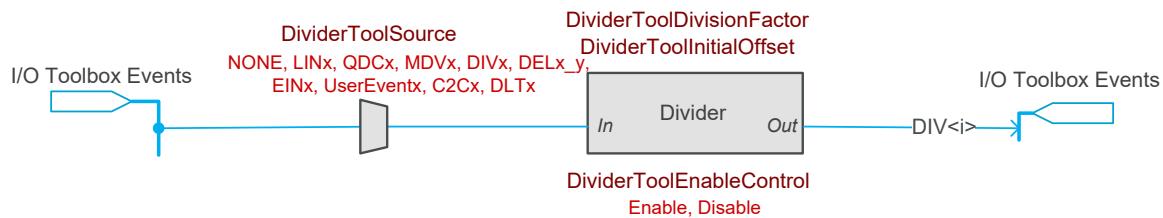

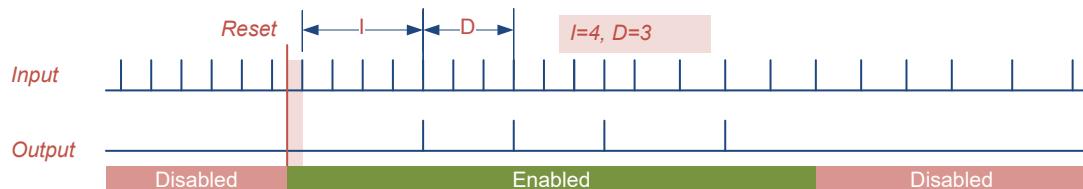

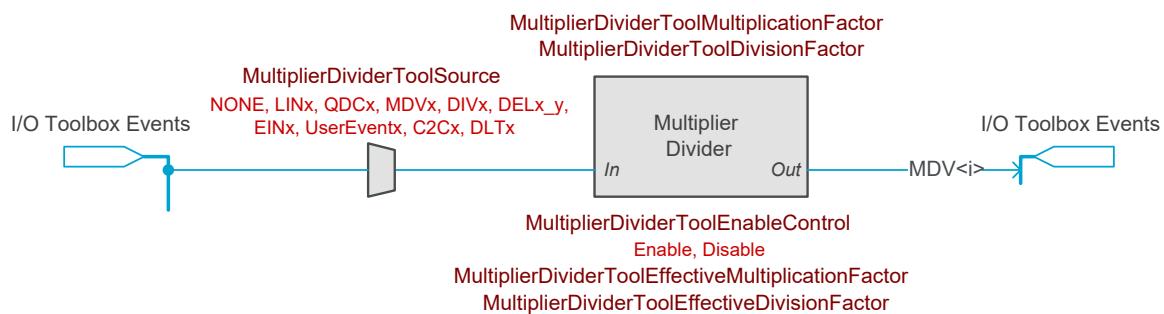

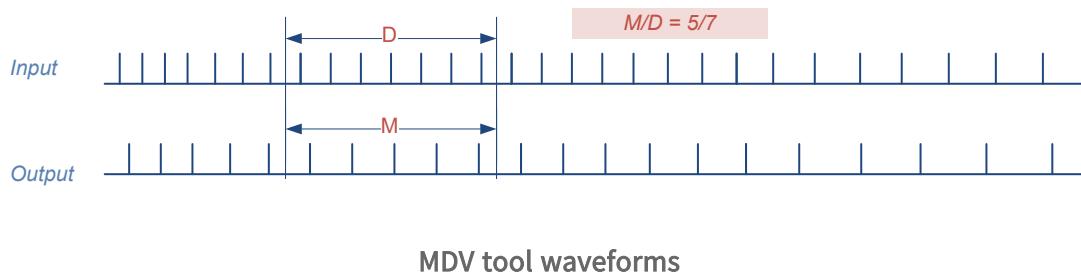

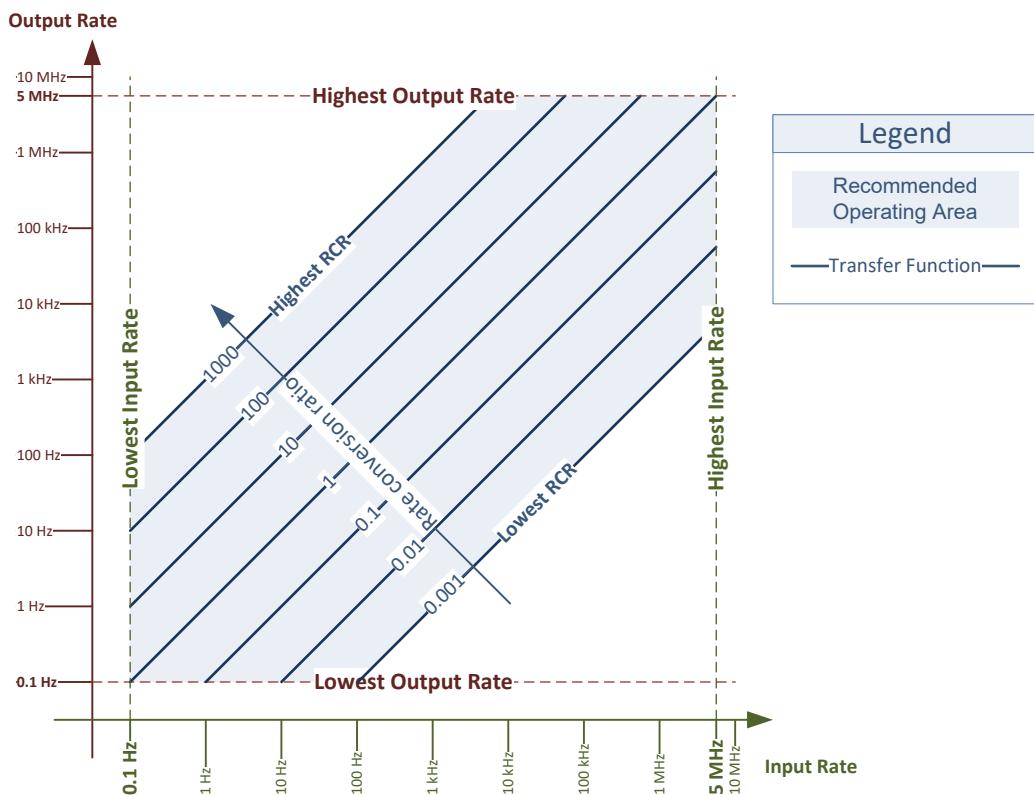

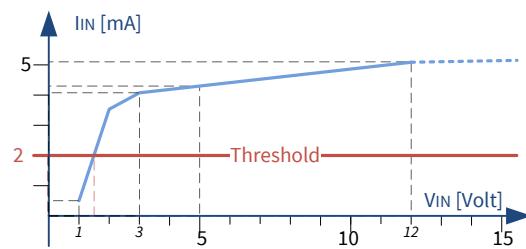

- The presence of a CoaXPress Device